## **FQM1 Series**

**FQM1-CM002**

FQM1-MMP22

FQM1-MMA22

# Flexible Motion Controller

# INSTRUCTIONS REFERENCE MANUAL

OMRON

#### Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

**!** DANGER

Indicates an imminently hazardous situation which, if not avoided, will result in death or serious injury. Additionally, there may be severe property damage.

/ WARNING

Indicates a potentially hazardous situation which, if not avoided, could result in death or serious injury. Additionally, there may be severe property damage.

Caution

Indicates a potentially hazardous situation which, if not avoided, may result in minor or moderate injury, or property damage.

#### **OMRON Product References**

All OMRON products are capitalized in this manual. The word "Unit" is also capitalized when it refers to an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation "Ch," which appears in some displays and on some OMRON products, often means "word" and is abbreviated "Wd" in documentation in this sense.

The abbreviation "CM" means Coordinator Module and the abbreviation "MM" means Motion Control Module.

## Visual Aids

The following headings appear in the left column of the manual to help you locate different types of information.

**Note** Indicates information of particular interest for efficient and convenient operation of the product.

1. Indicates lists of one sort or another, such as procedures, checklists, etc.

#### © OMRON, 2005

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

## Unit Versions of FQM1 Series Flexible Motion Controller

## **Unit Versions**

The FQM1 Series Controllers have "unit versions", which are used to manage the differences in functionality associated with upgrades to the Coordinator Modules and Motion Control Modules.

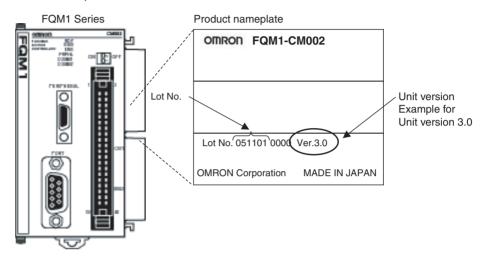

Notation of Unit Versions on Products

The unit version is listed just to the right of the lot number on the nameplate of the Module, as shown below.

#### **Unit Versions and Model Numbers**

| Name                  | Unit Ver. 2.0 | Unit Ver. 3.0            |

|-----------------------|---------------|--------------------------|

| Coordinator Module    | FQM1-CM001    | FQM1-CM002               |

| Motion Control Module |               | FQM1-MMA22<br>FQM1-MMP22 |

Note The Ver. 2.0 Modules (FQM1-CM001, FQM1-MMA21, and FQM1-MMP21) can be used together with the Ver. 3.0 Modules (FQM1-CM002, FQM1-MMA22, and FQM1-MMP22).

# Version Upgrade Guide

#### ■ Functional Improvements from Version 3.0 to Version 3.1

| Previous version (unit version 3.0) | Unit version 3.1 or later                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not UL listed                       | UL listed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                     | Note: For an FQM1-series Controller to conform to the UL listing, the system must be configured with an XW2B-80J7-1A Relay Unit and XW2Z-\Bullet \Bullet \Bull |

#### ■ Functional Improvements from Version 3.1 to Version 3.2

| Previous version (unit version 3.1)                                                                                                                                                              | Unit version 3.2 or later                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

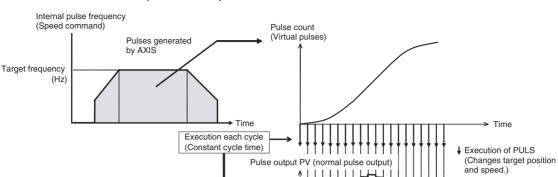

| Not in previous version                                                                                                                                                                          | When PULS(886) is used in electronic cam mode (ring), the pulse output can be set to pass through 0 in the CW direction or CCW direction.                                                                                                                                                      |

| When PULS(886) is used in electronic cam mode (linear or ring), the user set the present operation's reference position and pulse output frequency in the instruction's operands.                | When PULS(886) is used in electronic cam mode (linear or ring), a new option can be selected to automatically calculate the pulse output frequency based on the previous reference value and the present operation's reference value.                                                          |

| Not in previous version                                                                                                                                                                          | Two cyclic refreshing areas (up to 25 words each for output and input) can be added. These areas are primarily used as interface areas between the Coordinator Module and the base FB in the Motion Control Module. When the base FB is not being used, these areas can be used as work words. |

| Mounting CJ-series Units  Basic I/O Units (except the CJ1W-INT01 and CJ1W-IDP01)  CPU Bus Units: CJ1W-SPU01 and CJ1W-NCF71  Special I/O Units: CJ1W-SRM21  Communications Units: CJ1W-DRM21      | The following Units can be mounted, in addition to the Units listed on the left.  CPU Bus Units: CJ1W-ADG41  Special I/O Units: CJ1W-NC113/213/413/133/ 233/ 433, CJ1W-V600C11/V600C12  Note: The FQM1 Controllers do not support the IORD(222) and IOWR(223) instructions.                    |

| Not in previous version                                                                                                                                                                          | When the counter reset method is set to Phase-Z signal + software reset in the system settings, an interrupt task can be started when the counter is reset.                                                                                                                                    |

| When the 20-MHz clock is specified in the system settings for the pulse output function, the output frequency range is 400 Hz to 1 MHz.                                                          | When the 20-MHz clock is specified in the system settings, a new option can be selected to set an output frequency range of 1 Hz to 1 MHz.                                                                                                                                                     |

| When the high-speed analog sampling function is used with counter 1 as the sampling timing counter, the multiplier is always 1x, regardless of the counter 1 multiplier setting (1x, 2x, or 4x). | The sampling timing counter uses the same 1x, 2x, or 4x multiplier setting that is set for counter 1.                                                                                                                                                                                          |

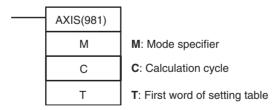

| The VIRTUAL AXIS (AXIS (981)) instruction's calculation cycle can be set to 0.5 ms, 1 ms, or 2 ms.                                                                                               | The calculation cycle settings have been expanded. The cycle can be set to 0.5 ms, 1 ms, 2 ms, 3 ms, or 4 ms.                                                                                                                                                                                  |

|                                                                                                                                                                                                  | The following conditions were removed from the conditions detected as errors when the instruction is executed.                                                                                                                                                                                 |

|                                                                                                                                                                                                  | <ul> <li>Target position (travel amount in relative mode) = 0</li> <li>Target position (target position in absolute mode) = Present position</li> <li>Target frequency &lt; Deceleration rate</li> </ul>                                                                                       |

#### ■ Functional Improvements from Version 3.2 to Version 3.3

| Previous version (unit version 3.2)                                 | Unit version 3.3 or later                                                                                                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OMNUC W-series Absolute Encoders can be used.                       | Absolute Encoders of OMNUC G-series Servomotors can be now be used (in addition to the Absolute Encoders of W-series Servomotors).                                                                                                                                                                                                  |  |

| CJ-series Units can be mounted.                                     | In addition to the Units that could previously be mounted, the following Special I/O Units can now be mounted.  • Analog Output Units: CJ1W-DA08V, CJ1W-DA08C, CJ1W-DA041, and CJ1W-DA021  • Analog Input Units: CJ1W-AD081-V1 and CJ1W-041-V1  • Analog I/O Unit: CJ1W-MAD42                                                       |  |

| The offset and gain of an analog output can be adjusted separately. | In addition to the previous functions, the default adjustment data can now be registered as the offset value for the analog output offset/gain adjustment function when adjusting the gain. This feature is useful for connecting to a Servo Driver, adjusting the offset using the Servo Driver, and then adjusting only the gain. |  |

# TABLE OF CONTENTS

| PRF  | CCAUTIONS                                       |

|------|-------------------------------------------------|

| 1    | Intended Audience                               |

| 2    | General Precautions                             |

| 3    | Safety Precautions                              |

| 4    | Conformance to EC Directives                    |

| 5    | Data Backup                                     |

| SEC  | CTION 1                                         |

|      | oduction                                        |

| 1-1  | General Instruction Characteristics             |

| 1-1  | Instruction Execution Checks                    |

|      |                                                 |

|      | CTION 2                                         |

| Sum  | mary of Instructions                            |

| 2-1  | Instruction Classifications by Function         |

| 2-2  | Instruction Functions.                          |

| 2-3  | Alphabetical List of Instructions by Mnemonic   |

| 2-4  | List of Instructions by Function Code           |

| SEC  | CTION 3                                         |

|      | ructions                                        |

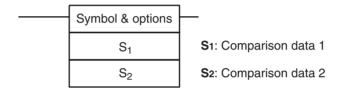

| 3-1  | Notation and Layout of Instruction Descriptions |

| 3-2  | Sequence Input Instructions                     |

| 3-3  | Sequence Output Instructions                    |

| 3-4  | Sequence Control Instructions                   |

| 3-5  | Timer and Counter Instructions.                 |

| 3-6  | Comparison Instructions                         |

| 3-7  | Data Movement Instructions                      |

| 3-8  | Data Shift Instructions                         |

| 3-9  | Increment/Decrement Instructions                |

| 3-10 |                                                 |

| 3-11 | Conversion Instructions.                        |

|      | Logic Instructions                              |

|      | Special Math Instructions                       |

|      | Floating-point Math Instructions                |

|      | Double-precision Floating-point Instructions    |

|      | Table Data Processing Instructions              |

|      | Data Control Instructions                       |

|      | Subroutines                                     |

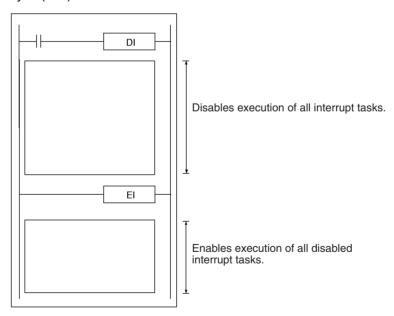

|      | Interrupt Control Instructions                  |

|      | High-speed Counter/Pulse Output Instructions.   |

|      | Step Instructions                               |

|      |                                                 |

## **TABLE OF CONTENTS**

| 3-22 | I/O Refresh Instruction                                                                                  | 580 |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 3-23 | Serial Communications Instructions                                                                       | 582 |

| 3-24 | Debugging Instructions                                                                                   | 596 |

| 3-25 | Failure Diagnosis Instructions                                                                           | 600 |

| 3-26 | Other Instructions                                                                                       | 606 |

| 3-27 | Block Programming Instructions                                                                           | 608 |

| 3-28 | Function Block Instructions.                                                                             | 618 |

|      | TION 4 ruction Execution Times and Number of Steps  FQM1 Instruction Execution Times and Number of Steps |     |

| Inde | X                                                                                                        | 639 |

| Revi | sion History                                                                                             | 645 |

### About this Manual:

This manual describes the ladder diagram programming instructions of the Coordinator Module and Motion Control Modules of the FQM1-series Flexible Motion Controllers.

Please read this manual and all related manuals listed in the table on the next page and be sure you understand information provided before attempting to program or use FQM1-series Flexible Motion Controllers in a control system.

| Name                                         | Cat. No. | Contents                                               |

|----------------------------------------------|----------|--------------------------------------------------------|

| FQM1 Series                                  | O012     | This manual provides an overview of and describes      |

| FQM1-CM002, FQM1-MMP22, FQM1-MMA22           |          | the following information for the FQM1-series Flexible |

| Flexible Motion Controllers Operation Manual |          | Motion Controllers: features, system configuration,    |

|                                              |          | system design, installation, wiring, maintenance, I/O  |

|                                              |          | memory allocation, troubleshooting, etc.               |

| FQM1 Series                                  | O013     | Describes the ladder diagram programming instruc-      |

| FQM1-CM002, FQM1-MMP22, FQM1-MMA22           |          | tions supported by FQM1-series Flexible Motion Con-    |

| Flexible Motion Controllers                  |          | trollers. Use this manual together with the Operation  |

| Instructions Reference Manual (this manual)  |          | Manual (Cat. No. O012).                                |

| SYSMAC WS02-CXPC1-E-V7                       | W446     | Provides information on how to use the CX-Program-     |

| CX-Programmer Operation Manual Version 7.x   |          | mer (except for function block functionality).         |

| SYSMAC WS02-CXPC1-E-V7                       | W447     | Provides specifications and operating procedures for   |

| CX-Programmer Operation Manual Version 7.x   |          | function blocks.                                       |

| Function Blocks                              |          |                                                        |

| SYSMAC CXONE-AL□□C-E                         | W445     | Provides an overview of the CX-One FA Integrated       |

| CX-One FA Integrated Tool Package Setup      |          | Tool and installation procedures.                      |

| Manual                                       |          |                                                        |

**Section 1** provides information on general instruction characteristics as well as the errors that can occur during instruction execution.

Section 2 provides summaries of instructions used with the FQM1.

Section 3 describes each of the instructions that can be used in programming the FQM1.

Section 4 provides instruction execution times and the number of steps for each FQM1 instruction.

#### Read and Understand this Manual

Please read and understand this manual before using the product. Please consult your OMRON representative if you have any questions or comments.

## Warranty and Limitations of Liability

#### WARRANTY

OMRON's exclusive warranty is that the products are free from defects in materials and workmanship for a period of one year (or other period if specified) from date of sale by OMRON.

OMRON MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, REGARDING NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR PARTICULAR PURPOSE OF THE PRODUCTS. ANY BUYER OR USER ACKNOWLEDGES THAT THE BUYER OR USER ALONE HAS DETERMINED THAT THE PRODUCTS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR INTENDED USE. OMRON DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED.

#### LIMITATIONS OF LIABILITY

OMRON SHALL NOT BE RESPONSIBLE FOR SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES, LOSS OF PROFITS OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE PRODUCTS, WHETHER SUCH CLAIM IS BASED ON CONTRACT, WARRANTY, NEGLIGENCE, OR STRICT LIABILITY.

In no event shall the responsibility of OMRON for any act exceed the individual price of the product on which liability is asserted.

IN NO EVENT SHALL OMRON BE RESPONSIBLE FOR WARRANTY, REPAIR, OR OTHER CLAIMS REGARDING THE PRODUCTS UNLESS OMRON'S ANALYSIS CONFIRMS THAT THE PRODUCTS WERE PROPERLY HANDLED, STORED, INSTALLED, AND MAINTAINED AND NOT SUBJECT TO CONTAMINATION, ABUSE, MISUSE, OR INAPPROPRIATE MODIFICATION OR REPAIR.

## **Application Considerations**

#### SUITABILITY FOR USE

OMRON shall not be responsible for conformity with any standards, codes, or regulations that apply to the combination of products in the customer's application or use of the products.

At the customer's request, OMRON will provide applicable third party certification documents identifying ratings and limitations of use that apply to the products. This information by itself is not sufficient for a complete determination of the suitability of the products in combination with the end product, machine, system, or other application or use.

The following are some examples of applications for which particular attention must be given. This is not intended to be an exhaustive list of all possible uses of the products, nor is it intended to imply that the uses listed may be suitable for the products:

- Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or uses not described in this manual.

- Nuclear energy control systems, combustion systems, railroad systems, aviation systems, medical

equipment, amusement machines, vehicles, safety equipment, and installations subject to separate

industry or government regulations.

- Systems, machines, and equipment that could present a risk to life or property.

Please know and observe all prohibitions of use applicable to the products.

NEVER USE THE PRODUCTS FOR AN APPLICATION INVOLVING SERIOUS RISK TO LIFE OR PROPERTY WITHOUT ENSURING THAT THE SYSTEM AS A WHOLE HAS BEEN DESIGNED TO ADDRESS THE RISKS, AND THAT THE OMRON PRODUCTS ARE PROPERLY RATED AND INSTALLED FOR THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

#### PROGRAMMABLE PRODUCTS

OMRON shall not be responsible for the user's programming of a programmable product, or any consequence thereof.

### **Disclaimers**

#### CHANGE IN SPECIFICATIONS

Product specifications and accessories may be changed at any time based on improvements and other reasons.

It is our practice to change model numbers when published ratings or features are changed, or when significant construction changes are made. However, some specifications of the products may be changed without any notice. When in doubt, special model numbers may be assigned to fix or establish key specifications for your application on your request. Please consult with your OMRON representative at any time to confirm actual specifications of purchased products.

#### **DIMENSIONS AND WEIGHTS**

Dimensions and weights are nominal and are not to be used for manufacturing purposes, even when tolerances are shown.

#### PERFORMANCE DATA

Performance data given in this manual is provided as a guide for the user in determining suitability and does not constitute a warranty. It may represent the result of OMRON's test conditions, and the users must correlate it to actual application requirements. Actual performance is subject to the OMRON Warranty and Limitations of Liability.

#### **ERRORS AND OMISSIONS**

The information in this manual has been carefully checked and is believed to be accurate; however, no responsibility is assumed for clerical, typographical, or proofreading errors, or omissions.

## **PRECAUTIONS**

This section provides general precautions for using the FQM1-series Flexible Motion Controllers and related devices.

The information contained in this section is important for the safe and reliable application of the FQM1-series Flexible Motion Controller. You must read this section and understand the information contained before attempting to set up or operate a control system using the FQM1-series Flexible Motion Controller.

| 1 | Intend              | led Audience                         | xviii |  |  |  |

|---|---------------------|--------------------------------------|-------|--|--|--|

| 2 | General Precautions |                                      |       |  |  |  |

| 3 | Safety              | Precautions                          | xviii |  |  |  |

|   | 3-1                 | Operating Environment Precautions    | xix   |  |  |  |

|   | 3-2                 | Application Precautions              | XX    |  |  |  |

| 4 | Confo               | ormance to EC Directives             | xxiii |  |  |  |

|   | 4-1                 | Applicable Directives                | xxiii |  |  |  |

|   | 4-2                 | Concepts                             | xxiii |  |  |  |

|   | 4-3                 | Conformance to EC Directives         | xxiii |  |  |  |

|   | 4-4                 | EMC Directive Conformance Conditions | xxiii |  |  |  |

|   | 4-5                 | Relay Output Noise Reduction Methods | xxiv  |  |  |  |

| 5 | Data I              | Backup                               | XXV   |  |  |  |

Intended Audience 1

#### **Intended Audience** 1

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

- · Personnel in charge of installing FA systems.

- Personnel in charge of designing FA systems.

- Personnel in charge of managing FA systems and facilities.

#### **General Precautions** 2

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, petrochemical plants, and other systems, machines, and equipment that may have a serious influence on lives and property if used improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are sufficient for the systems, machines, and equipment, and be sure to provide the systems, machines, and equipment with double safety mechanisms.

/!\ WARNING It is extremely important that the FQM1 be used for the specified purpose and under the specified conditions, especially in applications that can directly or indirectly affect human life. You must consult with your OMRON representative before applying an FQM1 System to the above-mentioned applications.

#### 3 **Safety Precautions**

/!\ WARNING Do not attempt to take any Modules apart while the power is being supplied. Doing so may result in electric shock.

/!\ WARNING Do not touch any of the terminals or terminal blocks while the power is being supplied. Doing so may result in electric shock.

/!\ WARNING Do not attempt to disassemble, repair, or modify any Modules. Any attempt to do so may result in malfunction, fire, or electric shock.

/!\ WARNING Provide safety measures in external circuits, i.e., not in the Flexible Motion Controller (referred to as the "FQM1"), to ensure safety in the system if an abnormality occurs due to malfunction of the FQM1 or another external factor affecting the FQM1 operation. Not doing so may result in serious accidents.

- Emergency stop circuits, interlock circuits, limit circuits, and similar safety measures must be provided in external control circuits.

- The FQM1 will turn OFF all outputs when its self-diagnosis function detects any error or when a severe failure alarm (FALS) instruction is executed. As a countermeasure for such errors, external safety measures must be provided to ensure safety in the system.

- The FQM1 outputs may remain ON or OFF due to destruction of the output transistors. As a countermeasure for such problems, external safety measures must be provided to ensure safety in the system.

> • When the 24-VDC output (service power supply to the FQM1) is overloaded or short-circuited, the voltage may drop and result in the outputs being turned OFF. As a countermeasure for such problems, external safety measures must be provided to ensure safety in the system.

/!\ WARNING Fail-safe measures must be taken by the customer to ensure safety in the event of incorrect, missing, or abnormal signals caused by broken signal lines, momentary power interruptions, or other causes. Not doing so may result in serious accidents.

/!\ Caution Execute online edit only after confirming that no adverse effects will be caused by extending the cycle time. Otherwise, the input signals may not be readable.

/!\ Caution User programs and parameters written to the Coordinator Module or Motion Control Module will be automatically backed up in the FQM1 flash memory (flash memory function). The contents of I/O memory (including the DM Area). however, are not written to flash memory. Part of the DM Area used as a holding area when recovering from a power interruption is backed up using a super capacitor, but correct values will not be maintained if an error occurs that prevents memory backup. As a countermeasure for such problems, take appropriate measures in the program using the Memory Not Held Flag (A316.14) when externally outputting the contents of the DM Area.

(Caution Confirm safety at the destination Module before transferring a program to another Module or editing the I/O area. Doing either of these without confirming safety may result in injury.

/!\ Caution Tighten the screws on the terminal block of the AC Power Supply Unit to the torque specified in the operation manual. The loose screws may result in burning or malfunction.

/!\ Caution Do not touch the Power Supply Unit while the power is ON, and immediately after turning OFF the power. Touching hot surfaces may result in burning.

/!\ Caution Pay careful attention to the polarities (+/-) when wiring the DC power supply. A wrong connection may cause malfunction of the system.

#### 3-1 **Operating Environment Precautions**

/!\ Caution Do not operate the control system in the following places:

- · Locations subject to direct sunlight

- Locations subject to temperatures or humidity outside the range specified in the specifications

- Locations subject to condensation as the result of severe changes in temperature

- Locations subject to corrosive or flammable gases

- Locations subject to dust (especially iron dust) or salts

- Locations subject to exposure to water, oil, or chemicals

- Locations subject to shock or vibration

/!\ Caution Take appropriate and sufficient countermeasures when installing systems in the following locations:

- Locations subject to static electricity or other forms of noise

- Locations subject to strong electromagnetic fields

- Locations subject to possible exposure to radioactivity

- · Locations close to power supplies

/!\ Caution The operating environment of the FQM1 System can have a large effect on the longevity and reliability of the system. Improper operating environments can lead to malfunction, failure, and other unforeseeable problems with the FQM1 System. Make sure that the operating environment is within the specified conditions at installation and remains within the specified conditions during the life of the system.

#### 3-2 **Application Precautions**

/!\ WARNING Always heed these precautions. Failure to abide by the following precautions could lead to serious or possibly fatal injury.

- Always connect to a ground of 100 Ω or less when installing the FQM1. Not doing so may result in electric shock.

- Always connect to a ground of 100  $\Omega$  or less when short-circuiting the functional ground and line ground terminals of the Power Supply Unit, in particular.

- Always turn OFF the power supply to the FQM1 before attempting any of the following. Not turning OFF the power supply may result in malfunction or electric shock.

- Mounting or dismounting Power Supply Unit, Coordinator Module, Motion Control Module, I/O Control Module, CJ-series Units, and End Module

- Assembling the Modules

- · Setting DIP switches

- Connecting or wiring the cables

- Connecting or disconnecting the connectors

/!\ Caution Failure to abide by the following precautions could lead to faulty operation of the FQM1 or the system, or could damage the FQM1. Always heed these precautions.

- Always use the CX-Programmer (Programming Device for Windows) to create new cyclic tasks and interrupt tasks.

- The user program, parameter area data, and part of the DM Area in the Coordinator Module and Motion Control Modules is backed up in the builtin flash memory. Do not turn OFF the power supply to the FQM1 while the user program or parameter area data is being transferred. The data will not be backed up if the power is turned OFF.

- The FQM1 will start operating in RUN mode when the power is turned ON with the default settings (i.e., if the operating mode at power ON (startup mode) setting in the System Setup is disabled).

- Configure the external circuits so that the control power supply turns ON after the power supply to the FQM1 turns ON. If the power is turned ON in the opposite order, the built-in outputs and other outputs may momentarily malfunction and the control outputs may temporarily not operate correctly.

Outputs may remain ON due to a malfunction in the built-in transistor outputs or other internal circuits. As a countermeasure for such problems, external safety measures must be provided to ensure the safety of the system.

- Part of the DM Area (data memory) in the Motion Control Module is held using the super capacitor. Corrupted memory may prevent the correct values from being saved, however. Take appropriate measures in the ladder program whenever the Memory Not Held Flag (A316.14) turns ON, such as resetting the data in the DM Area.

- Part of the DM Area in the Coordinator Module is backed up in the built-in flash memory when transferring data from the CX-Programmer. Do not turn OFF the power to the FQM1 while data is being transferred. The data will not be backed up if the power is turned OFF.

- Confirm that no adverse effect will occur in the system before attempting any of the following. Not doing so may result in an unexpected operation.

- Changing the operating mode of the FQM1 (including setting the operating mode at startup)

- Force-setting/force-resetting any bit in memory

- Changing the present value of any word or any set value in memory

- Install external breakers and take other safety measures against short-circuiting in external wiring. Insufficient safety measures against short-circuiting may result in burning.

- Be sure that all the terminal screws and cable connector screws are tightened to the torque specified in the relevant manuals. Incorrect tightening torque may result in malfunction.

- Mount the Modules only after checking the connectors and terminal blocks completely.

- Before touching the Module, be sure to first touch a grounded metallic object in order to discharge any static built-up. Not doing so may result in malfunction or damage.

- Be sure that the terminal blocks, connectors, and other items with locking devices are properly locked into place. Improper locking may result in malfunction.

- Wire correctly according to the specified procedures.

- Always use the power supply voltage specified in the operation manuals.

An incorrect voltage may result in malfunction or burning.

- Take appropriate measures to ensure that the specified power with the rated voltage and frequency is supplied. Be particularly careful in places where the power supply is unstable. An incorrect power supply may result in malfunction.

- Leave the dust protective label attached to the Module when wiring. Removing the label may result in malfunction.

- Remove the dust protective label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction

- Use crimp terminals for wiring. Do not connect bare stranded wires directly to terminals. Connection of bare stranded wires may result in burning.

- Do not apply voltages to the built-in inputs in excess of the rated input voltage. Excess voltages may result in burning.

Do not apply voltages or connect loads to the built-in outputs in excess of the maximum switching capacity. Excess voltage or loads may result in burning.

- Disconnect the functional ground terminal when performing withstand voltage tests. Not disconnecting the functional ground terminal may result in burning.

- Wire correctly and double-check all the wiring or the setting switches before turning ON the power supply. Incorrect wiring may result in burning.

- Check that the DIP switches and data memory (DM) are properly set before starting operation.

- Check the user program for proper execution before actually running it on the Module. Not checking the program may result in an unexpected operation.

- Resume operation only after transferring to the new Module the contents

of the DM Areas, programs, parameters, and data required for resuming

operation. Not doing so may result in an unexpected operation.

- Do not pull on the cables or bend the cables beyond their natural limit. Doing either of these may break the cables.

- Do not place objects on top of the cables. Doing so may break the cables.

- Use the dedicated connecting cables specified in operation manuals to connect the Modules. Using commercially available RS-232C computer cables may cause failures in external devices or the Coordinator Module.

- Do not connect pin 6 (+5V) on the RS-232C port on the Coordinator Module to any external device other than the NT-AL001 or CJ1W-CIF11 Conversion Adapter. Doing so may result in damage to the external device and the Coordinator Module.

- When replacing parts, be sure to confirm that the rating of a new part is correct. Not doing so may result in malfunction or burning.

- When transporting or storing the product, cover the PCBs with electrically conductive materials to prevent LSIs and ICs from being damaged by static electricity, and also keep the product within the specified storage temperature range.

- Do not touch the mounted parts or the rear surface of PCBs because PCBs have sharp edges such as electrical leads.

- When connecting the Power Supply Unit, Coordinator Module, Motion Control Module, I/O Control Module, CJ-series Units, and End Module, slide the upper and lower sliders until a click sound is heard to lock them securely. Desired functionality may not be achieved unless Modules are securely locked in place.

- Be sure to mount the End Module supplied with the Coordinator Module to the rightmost Module. Unless the End Module is properly mounted, the FQM1 will not function properly.

- Make sure that parameters are set correctly. Incorrect parameter settings

may result in unexpected operations. Make sure that equipment will not

be adversely affected by the parameter settings before starting or stopping the FQM1.

#### 4 Conformance to EC Directives

#### 4-1 Applicable Directives

- EMC Directives

- · Low Voltage Directive

#### 4-2 Concepts

#### **EMC Directives**

OMRON devices that comply with EC Directives also conform to the related EMC standards so that they can be more easily built into other devices or the overall machine. The actual products have been checked for conformity to EMC standards (see the following note). Whether the products conform to the standards in the system used by the customer, however, must be checked by the customer.

EMC-related performance of the OMRON devices that comply with EC Directives will vary depending on the configuration, wiring, and other conditions of the equipment or control panel on which the OMRON devices are installed. The customer must, therefore, perform the final check to confirm that devices and the overall machine conform to EMC standards.

Note Applicable EMC (Electromagnetic Compatibility) standards are as follows:

EMS (Electromagnetic Susceptibility): EN61000-6-2 EMI (Electromagnetic Interference): EN61000-6-4

(Radiated emission: 10-m regulations)

#### **Low Voltage Directive**

Always ensure that devices operating at voltages of 50 to 1,000 V AC and 75 to 1,500 V DC meet the required safety standards for the Motion Controller (EN61131-2).

#### 4-3 Conformance to EC Directives

The FQM1-series Flexible Motion Controllers comply with EC Directives. To ensure that the machine or device in which the Motion Controller is used complies with EC Directives, the Motion Controller must be installed as follows:

- 1,2,3... 1. The Motion Controller must be installed within a control panel.

- You must use reinforced insulation or double insulation for the DC power supplies used for the communications power supply and I/O power supplies.

- 3. Motion Controllers complying with EC Directives also conform to the Common Emission Standard (EN61000-6-4). Radiated emission characteristics (10-m regulations) may vary depending on the configuration of the control panel used, other devices connected to the control panel, wiring, and other conditions. You must therefore confirm that the overall machine or equipment complies with EC Directives.

#### 4-4 EMC Directive Conformance Conditions

The immunity testing condition of the Motion Controller Modules is as follows: Overall accuracy of FQM1-MMA22 analog I/O: +4%/-2%

### 4-5 Relay Output Noise Reduction Methods

The FQM1-series Flexible Motion Controller conforms to the Common Emission Standards (EN61000-6-4) of the EMC Directives. However, noise generated by relay output switching may not satisfy these Standards. In such a case, a noise filter must be connected to the load side or other appropriate countermeasures must be provided external to the Motion Controller.

Countermeasures taken to satisfy the standards vary depending on the devices on the load side, wiring, configuration of machines, etc. Following are examples of countermeasures for reducing the generated noise.

#### **Countermeasures**

(Refer to EN61000-6-4 for more details.)

Countermeasures are not required if the frequency of load switching for the whole system with the Motion Controller included is less than 5 times per minute.

Countermeasures are required if the frequency of load switching for the whole system with the Motion Controller included is more than 5 times per minute.

#### **Countermeasure Examples**

When switching an inductive load, connect a surge protector, diodes, etc., in parallel with the load or contact as shown below.

| Circuit                                  | Current |     | Characteristic                                                                                                                                                                                                                                                                                                         | Required element                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                          | AC      | DC  |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| CR method  C   exitonpul  Power R   peol | Yes     | Yes | If the load is a relay or solenoid, there is a time lag between the moment the circuit is opened and the moment the load is reset.  If the supply voltage is 24 or 48 V, insert the surge protector in parallel with the load. If the supply voltage is 100 to 200 V, insert the surge protector between the contacts. | The capacitance of the capacitor must be 1 to $0.5~\mu F$ per contact current of 1 A and resistance of the resistor must be $0.5$ to 1 $\Omega$ per contact voltage of 1 V. These values, however, vary with the load and the characteristics of the relay. Decide these values from experiments, and take into consideration that the capacitance suppresses spark discharge when the contacts are separated and the resistance limits the current that flows into the load when the circuit is closed again. The dielectric strength of the capacitor must be 200 to 300 V. If the circuit is an AC circuit, use a capacitor with no polarity. |  |

| Circuit Current                             |     | rent | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                    | Required element                                                                                                                                                                                           |  |

|---------------------------------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                             | AC  | DC   |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                            |  |

| Diode method  Power  Power                  | No  | Yes  | The diode connected in parallel with the load changes energy accumulated by the coil into a current, which then flows into the coil so that the current will be converted into Joule heat by the resistance of the inductive load.                                                                                                                                                                                | The reversed dielectric strength value of the diode must be at least 10 times as large as the circuit voltage value. The forward current of the diode must be the same as or larger than the load current. |  |

| supply                                      |     |      | This time lag, between the moment the circuit is opened and the moment the load is reset, caused by this method is longer than that caused by the CR method.                                                                                                                                                                                                                                                      | The reversed dielectric strength value of the diode may be two to three times larger than the supply voltage if the surge protector is applied to electronic circuits with low circuit voltages.           |  |

| Varistor method  Power supply  Power supply | Yes | Yes  | The varistor method prevents the imposition of high voltage between the contacts by using the constant voltage characteristic of the varistor. There is time lag between the moment the circuit is opened and the moment the load is reset.  If the supply voltage is 24 or 48 V, insert the varistor in parallel with the load. If the supply voltage is 100 to 200 V, insert the varistor between the contacts. |                                                                                                                                                                                                            |  |

When switching a load with a high inrush current such as an incandescent lamp, suppress the inrush current as shown below.

Providing a dark current of approx. one-third of the rated value through an incandescent lamp

#### Countermeasure 2

Providing a limiting resistor

The following Unit and Cables can be used with the FQM1-series Flexible Motion Controller.

| Name                | Model         | Cable length |

|---------------------|---------------|--------------|

| Relay Unit          | XW2B-80J7-1A  |              |

| Controller Connect- | XW2Z-050J-A28 | 0.5 m        |

| ing Cables          | XW2Z-100J-A28 | 1 m          |

|                     | XW2Z-050J-A30 | 0.5 m        |

|                     | XW2Z-100J-A30 | 1 m          |

|                     | XW2Z-050J-A31 | 0.5 m        |

|                     | XW2Z-100J-A31 | 1 m          |

Data Backup 5

## 5 Data Backup

The user programs, I/O memories, and other data in the Coordinator Module and Motion Control Modules is backed up either by a super capacitor or flash memory, as listed in the following table.

| Module                | Data                                                             | Data backup    |

|-----------------------|------------------------------------------------------------------|----------------|

| Coordinator Module    | Error log                                                        | RAM with super |

| Motion Control Module | DM Area words D30000 to D32767                                   | capacitor      |

|                       | Error log                                                        |                |

| Coordinator Module    | User program                                                     | Flash memory   |

|                       | System Setup                                                     |                |

|                       | DM Area words D20000 to D32767                                   |                |

| Motion Control Module | User program                                                     |                |

|                       | System Setup                                                     |                |

|                       | DM Area words D00000 to D29999 (Auxiliary Area bit must be set.) |                |

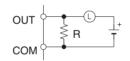

The data backup time of the super capacitor is given in the following table and shown in the following graph.

| Temperature | Initial                     | After 5 years | After 10 years            |

|-------------|-----------------------------|---------------|---------------------------|

| Ta = 25°C   | 101.61 hours<br>(4.23 days) |               | 90.8 hours<br>(3.78 days) |

| Ta = 40°C   | 26.39 hours<br>(1.09 days)  | 15.28 hours   | 4.16 hours                |

Super Capacitor Backup Times

Note 1. The times give above assume that the capacitor is completely charged. Power must be supply to the FQM1 for at least 20 minutes to completely charge the capacitor.

Data Backup 5

2. The backup time of the super capacitor is reduced as the capacitor ages. It is also affected by the ambient temperature. Use portion of the DM Area backed up by the super capacitor only for data that is to be held during momentary power interruptions. For operating parameters and other long-term data, use the portion of DM Area stored in flash memory in the Coordinator Module and transfer it to the Motion Control Modules before starting operation.

The data in the DM Area and error log will become unstable or corrupted if the power to the system is OFF for longer than the backup time.

If the power supply is to be turned OFF for an extended period of time, use D20000 to D32767 in the Coordinator Module and D00000 to D29999 in the Motion Control Module, which is backed up in flash memory, to store data.

Otherwise, the Memory Not Held Flag (A316.14) can be used as the input condition for programming using data in areas stored for power interruptions to perform suitable processing.

A316.14: Turns ON when power is turned ON if data stored for power interruptions in the DM Area or error log is corrupted.

```

Processing for corruption of data backed up for power interruptions

```

#### **Backing Up DM Area Data in Flash Memory**

DM Area words D20000 to D32767 for the Coordinator Module and D00000 to D29999 for the Motion Control Modules are read from flash memory when the power supply is turned ON. (A Setup parameter must be set to read DM Area data for the Motion Control Modules.)

# **SECTION 1 Introduction**

This section provides information on general instruction characteristics as well as the errors that can occur during instruction execution.

| 1-1 | Genera   | l Instruction Characteristics                 | 2 |

|-----|----------|-----------------------------------------------|---|

|     | 1-1-1    | Program Capacity                              | 2 |

|     | 1-1-2    | Differentiated Instructions                   | 2 |

|     | 1-1-3    | Instruction Variations                        | 3 |

|     | 1-1-4    | Instruction Location and Execution Conditions | 3 |

|     | 1-1-5    | Inputting Data in Operands                    | 4 |

|     | 1-1-6    | Data Formats                                  | 7 |

| 1-2 | Instruct | tion Execution Checks                         | 8 |

|     | 1-2-1    | Errors Occurring at Instruction Execution     | 8 |

|     | 1-2-2    | Fatal Errors (Program Errors)                 | 9 |

#### 1-1 General Instruction Characteristics

#### 1-1-1 **Program Capacity**

The program capacity tells the size of the user program area each Module and is expressed as the number of program steps. The number of steps required in the user program area for each instruction varies from 1 to 7 steps, depending upon the instruction and the operands used with it.

| Model                            |            | Model      | Program capacity |

|----------------------------------|------------|------------|------------------|

| Coordinator Module               |            | FQM1-CM002 | 10K steps        |

| Motion Control Modules Pulse I/O |            | FQM1-MMP22 |                  |

|                                  | Analog I/O | FQM1-MMA22 |                  |

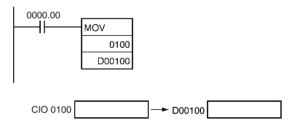

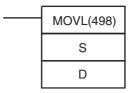

Note The number of steps in a program is not the same as the number of instructions, i.e., each instruction contains from 1 to 7 steps. For example, LD and OUT require 1 step each, but MOV(021) requires 3 steps. The number of steps required by an instruction is also increased by one step for each doublelength operand used in it. For example, MOVL(498) normally requires 3 steps, but 4 steps will be required if a constant is specified for the source word operand, S. Refer to SECTION 4 Instruction Execution Times and Number of Steps for the number of steps required for each instruction.

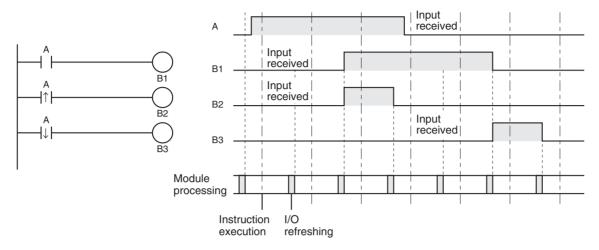

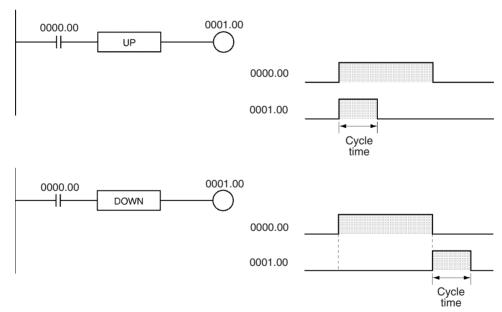

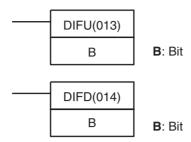

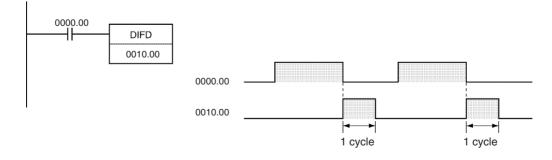

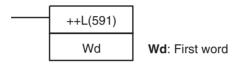

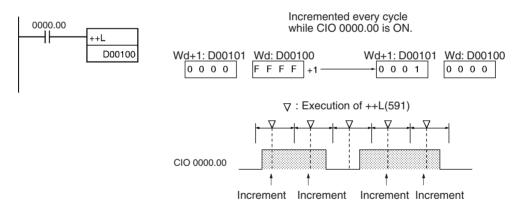

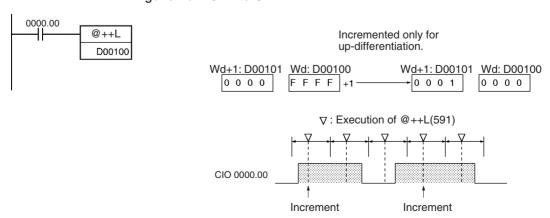

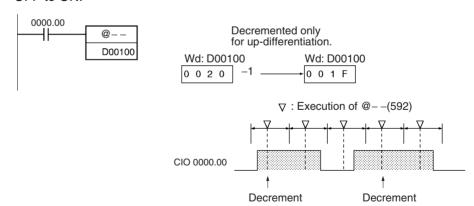

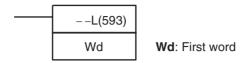

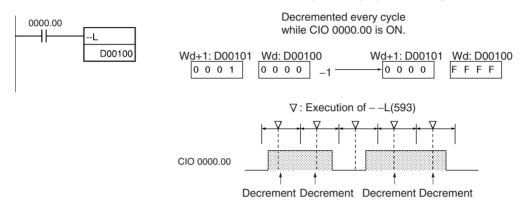

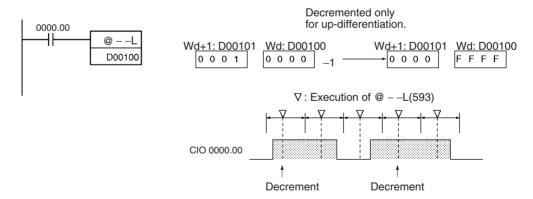

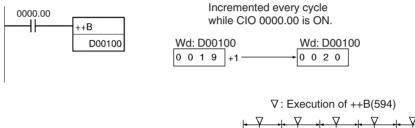

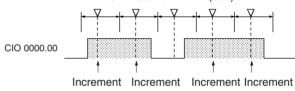

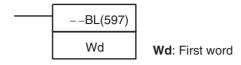

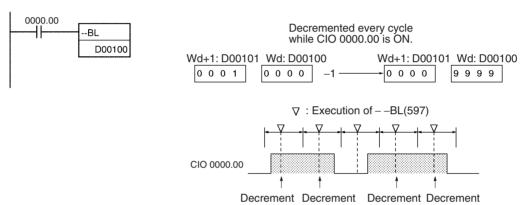

#### 1-1-2 **Differentiated Instructions**

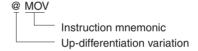

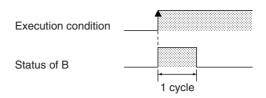

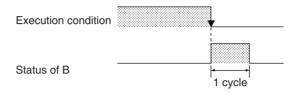

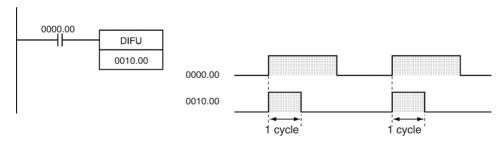

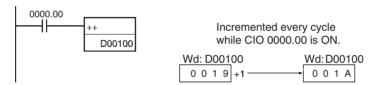

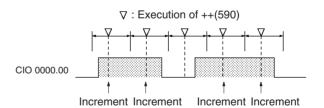

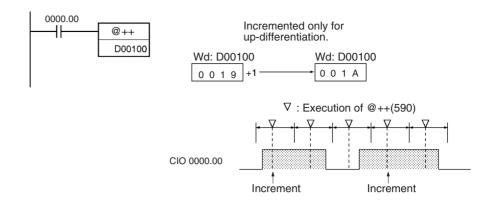

Most instructions in the FQM1 are provided with both non-differentiated and upwardly differentiated variations, and some are also provided with downwardly differentiated variations.

- A non-differentiated instruction is executed every time it is scanned.

- An upwardly differentiated instruction is executed only once after its execution condition goes from OFF to ON.

- A downwardly differentiated instruction is executed only once after its execution condition goes from ON to OFF.

| Variation                                     | Instruction type                                                               | Operation                                                                                                                                                           | Format                                                | Example                                                                                         |

|-----------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Non-<br>differentiated                        | Output instructions<br>(instructions requiring<br>an execution condi-<br>tion) | The instruction is executed every cycle while the execution condition is true (ON).                                                                                 | Output instruction executed each cycle                | Н-[моv ]—                                                                                       |

|                                               | Input instructions<br>(instructions used as<br>execution conditions)           | The bit processing (such as read, comparison, or test) is performed every cycle. The execution condition is true while the result is ON.                            | Input instruction executed each cycle                 | <u></u>                                                                                         |

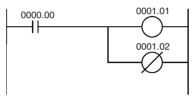

| Upwardly<br>differentiated<br>(with @ prefix) | Output instructions                                                            | The instruction is executed just once when the execution condition goes from OFF to ON.                                                                             | @Instruction executed once for upward differentiation | MOV(021) executed once for each OFF to ON transition in CIO 0001.02.                            |

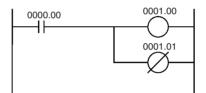

|                                               | Input instructions<br>(instructions used as<br>execution conditions)           | The bit processing (such as read, comparison, or test) is performed every cycle. The execution condition is true for one cycle when the result goes from OFF to ON. | Upwardly differentiated input instruction             | ON execution condition created for one cycle only for each OFF to ON transition in CIO 0001.03. |

| Variation                                       | Instruction type                                                     | Operation                                                                                                                                                           | Format                                                  | Example                                                                                         |

|-------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|

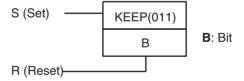

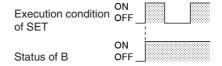

| Downwardly<br>differentiated<br>(with % prefix) | Output instructions                                                  | The instruction is executed just once when the execution condition goes from ON to OFF.                                                                             | %Instruction executed once for downward differentiation | 0001.02 SET executed once for each ON to OFF transition in CIO 0001.02.                         |

|                                                 | Input instructions<br>(instructions used as<br>execution conditions) | The bit processing (such as read, comparison, or test) is performed every cycle. The execution condition is true for one cycle when the result goes from ON to OFF. | Downwardly differentiated input instruction             | ON execution condition created for one cycle only for each ON to OFF transition in CIO 0001.03. |

**Note** The downwardly differentiated option (%) is available only for the LD, AND, OR, and RSET instructions. To create downwardly differentiated variations of other instructions, control the execution of the instruction with work bits controlled with DIFD(014).

#### 1-1-3 Instruction Variations

The variation prefixes (@ and %) can be added to certain instructions to create a differentiated instruction.

| Variation       |                              | Prefix | Operation                                        |

|-----------------|------------------------------|--------|--------------------------------------------------|

| Differentiation | Upwardly dif-<br>ferentiated | @      | Creates an upwardly differentiated instruction.  |

|                 | Downwardly differentiated    | %      | Creates a downwardly differentiated instruction. |

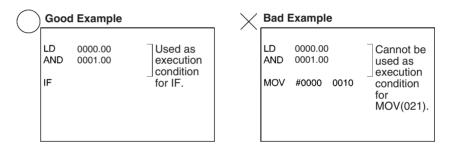

#### 1-1-4 Instruction Location and Execution Conditions

The following table shows the locations in which instructions can be programmed. The table also shows when an instruction requires an execution condition and when it does not. Refer to SECTION 2 Summary of Instructions for details on specific instructions.

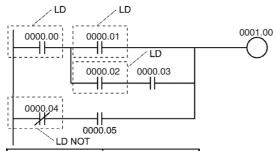

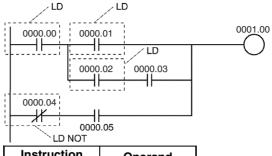

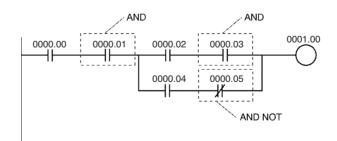

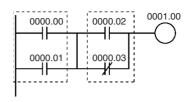

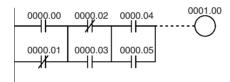

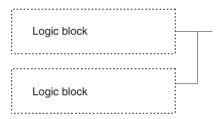

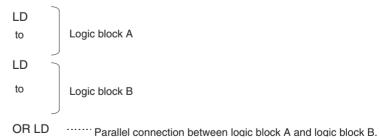

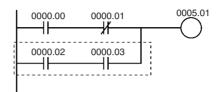

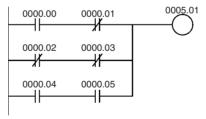

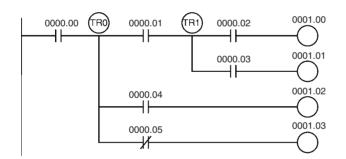

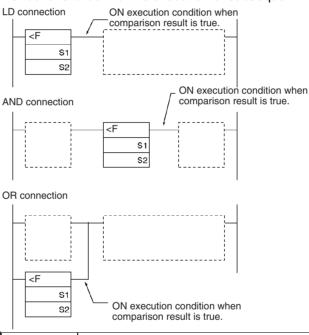

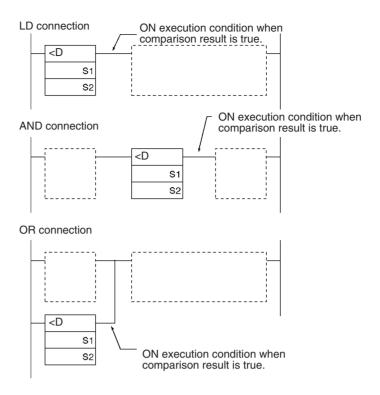

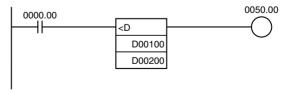

| Ins    | truction type                                                | Location                                              | Execution condition | Format                                          | Examples                                                  |

|--------|--------------------------------------------------------------|-------------------------------------------------------|---------------------|-------------------------------------------------|-----------------------------------------------------------|

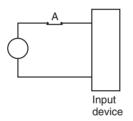

| Input  | Instructions that start logic conditions (load instructions) | start of an instruction                               | Not<br>required     | Hami                                            | LD and input comparison instructions such as LD >         |

|        | Connecting instructions                                      | Between a starting instruction and output instruction | Required            | 1                                               | AND, OR, and input comparison instructions, such as AND > |

| Output | i                                                            | At the right bus                                      | Required            | <del>                                    </del> | The majority of instructions (such as OUT and MOV)        |

|        |                                                              |                                                       | Not required        |                                                 | Instructions such as END, JME, and ILC                    |

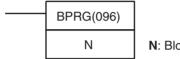

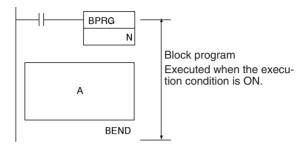

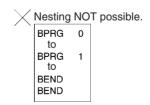

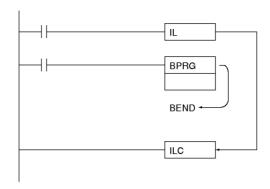

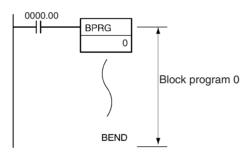

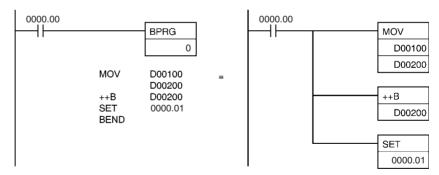

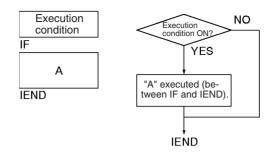

In addition to these instructions, the FQM1 is equipped with block programming instructions. Refer to the description of the block programming instructions for details.

**Note** If an execution condition does not precede an instruction that requires one, a program error will occur when the program is checked from the CX-Programmer.

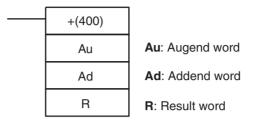

## 1-1-5 Inputting Data in Operands

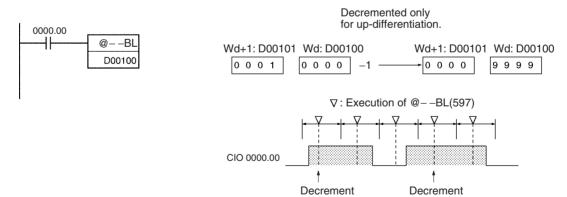

Operands are parameters that are set in advance with the I/O memory addresses or constants to be used when the instruction is executed. There are basically three kinds of operands: Source operands, destination operands, and numbers.

| Operand     |                                                                | Usual<br>code |                 | Contents                                                          |

|-------------|----------------------------------------------------------------|---------------|-----------------|-------------------------------------------------------------------|

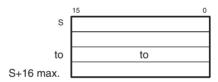

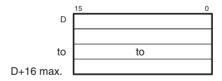

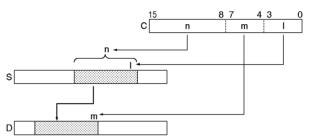

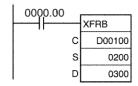

| Source      | Address containing the data or the data                        | S             | Source operand  | Source data other than control data                               |

| itself      |                                                                | С             | Control<br>data | Control data with a bit or bits controlling instruction execution |

| Destination | Address where the data will be stored                          | D             |                 |                                                                   |

| Number      | Contains a number, such as a jump number or subroutine number. | N             |                 |                                                                   |

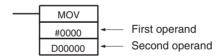

**Note** An instruction's operands may also be referred to by their position in the instruction (first operand, second operand, ...). The codes used for the operand vary with the specific function of the operand.

#### **Specifying Bit Addresses**

| Description                                                                                                       | Example                                | Instruction example       |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|

| To specify a bit address, specify the word address and bit address directly.  Bit number (00 to 15)  Word address | 0001.02<br>— Bit 02<br>— Word CIO 0001 | 0001<br>02<br>├─ <b>│</b> |

| Note The word address + bit number format is not used for Timer/Counter Completion Flags or Task Flags.           |                                        |                           |

#### **Specifying Word Addresses**

| Description                                                                               | Example                       | Instruction example |

|-------------------------------------------------------------------------------------------|-------------------------------|---------------------|

| To specify a word address, specify the word address directly. Each word contains 16 bits. | 0003<br>Word CIO 0003         | MOV 0003 D00200     |

| Word address                                                                              | D <u>00200</u><br>Word D00200 |                     |

#### **Specifying Indirect DM Addresses in Binary Mode**

| Description                                                                                                                                                                                                                             | Example                                                               | Instruction example |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------|

| When the @ prefix is input before a DM address, the contents of that word specifies another word that is used as the operand. The contents can be 0000 to 7FFF (0 to 32,767), corresponding to the desired word address in the DM Area. |                                                                       |                     |

| @ <u>D                                   </u>                                                                                                                                                                                           |                                                                       |                     |

| Content 00000 to 32767 (0000 to 7FFF)                                                                                                                                                                                                   |                                                                       |                     |

| When the contents of @DDDDDD is between 0000 and 7FFF (00000 to 32,767), the corresponding word between D00000 and D32767 is specified.                                                                                                 | @ D00300  0 1 0 0  Decimal: 256  Specifies D00256.  Add the @ prefix. | MOV #0001 @ D00300  |

#### **Specifying Indirect DM Addresses in BCD Mode**

| Method                                  | Description                                                                                                                                                                                                                                                       | Example                                                | Instruction example |

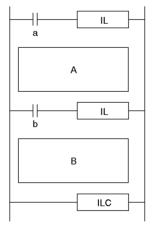

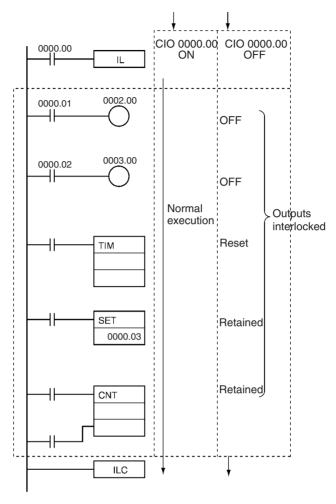

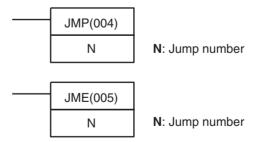

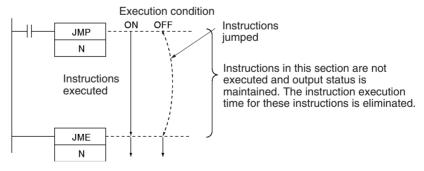

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------|