# SYSMAC Programmable Controller

C500

# OPERATION MANUAL

OMRON

#### Preface

The Omron C500 PC offers an effective way to automate many types of processes such as manufacturing, assembly, and packaging, to save time and money. The PC is fully equipped with facilities such as programming instructions and data areas, to control these processes directly, or remotely. Distributed control systems can be designed to allow centralized monitoring and supervision of several separate controlled systems. Monitoring and supervising can also be done through a host computer, connecting the controlled system to the data bank. Thus, it is possible to to have adjustments in system operation made automatically to compensate for requirement changes.

This manual describes the characteristics and abilities of the PC, as well as the aspects of operation and preparation that demand attention. Before attempting to operate the PC, thoroughly familiarize yourself with the information contained herein.

© Omron, 1988

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, electronic, photocopying, or otherwise, without the prior written permission of Omron.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because Omron is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without notice. Every precaution has been taken in the preparation of this manual.

Nevertheless, Omron assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

## **Corrections Insert**

Manual:

SYSMAC Programmable Controller C500 Operation Manual

Catalog No.:

W131-E1-1

Corrected Catalog No.: W131-E1-1A

Date:

**April 1995**

This corrections insert lists corrections made to this manual since it was printed. Only corrections that affect the proper and efficient operation of the device are listed; minor changes, such as those in spelling and syntax, have been omitted.

Please mark your manuals so that the corrections are noted on the pages concerned, and then securely add any required pages from the Corrections Insert to the rear of the manual.

#### • Page20

Add the following subsection.

#### **Battery-free Operation**

Operation without a battery is possible by placing the user program and I/O table data on PROM. Note the following precautions before attempting battery-free operation.

Data will be handled as described below when operating without a battery or with a discharged battery.

- HR area, T/C area (present values), and DM area value will not be preserved during power interruptions.

- SR area data will not be stable during power interruptions.

To prevent problems that can occur in the above data, write the following instructions into the beginning of the user program to clear the load-off control (SR 6015) and the data retention flag (SR 6012).

| Address | Instruction | Operands |

|---------|-------------|----------|

| 0000    | LD          | 6115     |

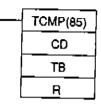

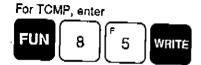

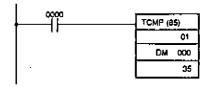

| 0001    | TCMP(85)    |          |

|         |             | #6FFF    |

|         |             | 60       |

|         | `           | 60       |

Use the following procedure to write the PROM.

- 1, 2, 3...

- 1. Write the user program to a RAM Memory Unit.

- 2. Register the I/O table using the procedure on page 28.

- 3. Transfer the I/O table using the procedure on page 33. You can specify during the transfer procedure not to detect low battery voltage as an error.

- Transfer the contents of the RAM to PROM using a PROM writer.

#### Pages 83 and 86

Add the following note.

Note HR, T/C, and DM area data is backed up during power interruptions via the battery in the CPU. If this battery is missing or the voltage is low, HR, T/C, and DM area data may be lost during power interruptions.

#### Corrections Insert: W131-E1-1A

#### Page 184

Add the following information.

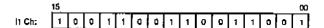

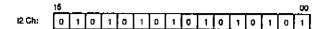

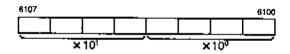

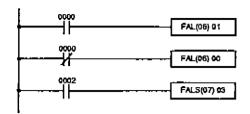

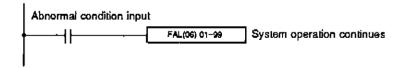

FAL numbers are recorded in memory as they occur. The contents of the three FAL numbers in memory is as follows:

1st FAL number: First FAL number to be generated.

2nd FAL number: Smallest FAL number of all FAL numbers that have

been generated larger than the first FAL number.

3rd FAL number: Smallest FAL number of all FAL numbers that have .

been generated smaller than the first FAL number.

#### Page 189

Add the following note.

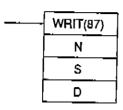

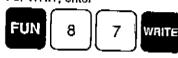

Note If the Intelligent I/O Unit is busy when WRIT (87) is executed, execution will not be carried out until the next scan when the Unit is not busy. Use a self-holding bit to ensure that the execution condition for WRIT (87) remains ON until it is executed.

#### Page 192 <sup>7</sup>

Add the following note.

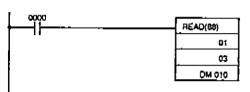

Note If the read data is not ready or the Intelligent I/O Unit is busy when READ (88) is executed, execution will not be carried out until at least the next scan. Use a self-holding bit to ensure that the execution condition for READ (88) remains ON until it is executed.

#### Pages 222 and 223

Add the following error to the end of the table. All columns not given below are blank (----) in the table and have been omitted here.

| ltem                        | Error display | Main cause of error            | Corrections                                                                                |

|-----------------------------|---------------|--------------------------------|--------------------------------------------------------------------------------------------|

| Contradictory mode settings |               | switch is not set for the host | Set the Programming<br>Console switch for the host<br>link and then input the<br>password. |

#### Page 229

Add the following CPU Backplane Power Supply to the table.

| Name                          | Remarks |                      | Model        |

|-------------------------------|---------|----------------------|--------------|

| CPU Backplane<br>Power Supply | 24 VDC  | Output: 7 A at 5 VDC | C500-PS213-E |

#### Page 237

Correct the model number of the Peripheral Interface Unit to C200H-IP006.

Delete all of the GPC models except for the 3G2C5-GPC03-E.

#### • Page 237 and 239

Add the following information on the most current Support Software (programming software).

LSS

The most current versions of the LSS are the C500-SF711-EV3 (2D 5" disks)

and the C500-SF312-EV3 (2HD 3.5" disks).

SSS

The most advanced Support Software offered by OMRON is the SYSMAC Support Software (SSS: C500-ZL3AT-E, 2HD 3.5" disks). The SSS runs on an IBM PC/AT or compatible and supports both C-series PCs and CVM1 PC.

### **TABLE OF CONTENTS**

| SECTION 1 |                                                        |    |

|-----------|--------------------------------------------------------|----|

|           | <u>ng</u>                                              |    |

|           | Relay Circuits: The Roots of PC Logic                  |    |

| 1-2       | Basic Programming Steps                                |    |

|           | 1-2-1 Assessing the Control Task                       |    |

|           | 1-2-2 Drawing the Ladder Diagram                       | 4  |

|           | 1-2-3 Converting the Ladder Diagram into Mnemonic Code | 4  |

| 1-3       | Basic Programming Instructions                         |    |

| ,         | (LD, OUT, AND, OR, NOT, and END)                       | 6  |

|           | 1-3-1 AND LD and OR LD                                 | 6  |

| 1-4       | Programming Techniques                                 | 10 |

|           | 1-4-1 Program Organization                             |    |

|           | 1-4-2 Programming Examples,                            | 13 |

| SECTION 2 |                                                        |    |

|           | <u>ole</u>                                             | 21 |

| 2-1       | The Programming Console ,,,,,,,,                       | 21 |

|           | 2-1-1 The Keyboard                                     | 22 |

|           | 2-1-2 The Mode Switch                                  | 23 |

|           | 2-1-3 The Display Message Switch                       | 24 |

| 2-2       | Preparation for Programming                            | 25 |

|           | 2-2-1 Entering the Password                            | 25 |

|           | 2-2-2 Clear Memory                                     | 26 |

|           | 2-2-3 Registering the VO Table                         | 28 |

|           | 2-2-4 Verilying the I/O Table                          | 29 |

|           | 2-2-5 Reading the I/O Table                            | 30 |

|           | 2-2-6 Transferring the I/O Table                       | 33 |

| 2-3       | Programming Operations                                 | 35 |

|           | 2-3-1 Setting a Program Address                        |    |

|           | 2-3-2 Program Read                                     |    |

|           | 2-3-3 Instruction Search                               |    |

|           | 2-3-4 Bit Search                                       |    |

|           | 2-3-5 Instruction Insert                               |    |

|           | 2-3-6 Instruction Delete                               |    |

|           | 2-3-7 Program Check                                    |    |

|           | 2-3-8 Scan Time Read                                   |    |

|           | 2-3-9 Error Message Read                               |    |

| 2-4       | Monitor Operations                                     |    |

|           | 2-4-1 General Status Monitoring                        |    |

|           | 2-4-2 Displaying a Single Channel in Binary            |    |

| T.                      | 2-5 Data Modification Operations           | 55 |

|-------------------------|--------------------------------------------|----|

|                         | 2-5-1 Force Set/Reset                      |    |

|                         | 2-5-2 PV Change 1                          | 57 |

|                         | 2-5-3 PV Change 2                          |    |

|                         | 2-5-4 Timer/Counter SV Change 1            | 60 |

|                         | 2-6 Cassette Tape Operations               | 61 |

|                         | 2-6-1 Saving a Program to Tape             |    |

|                         | 2-6-2 Restoring Program Data               |    |

|                         | 2-6-3 Verifying Program Data               |    |

|                         |                                            | •  |

|                         |                                            | 1  |

| SECTION 3               |                                            |    |

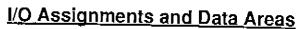

| I/O Assignments and Da  | <u>ta Areas</u>                            | 69 |

|                         | 3-1 Overview                               | 69 |

|                         | 3-2 I/O and Internal Relay Area - IR       | 71 |

|                         | 3-3 Special Relay Area - SR                | 76 |

|                         | 3-3-1 Data Retention Flag                  | 77 |

|                         | 3-3-2 Load Off Control                     | 77 |

|                         | 3-3-3 FAL Number Output Area               | 77 |

|                         | 3-3-4 Battery Alarm Flag                   | 78 |

|                         | 3-3-5 Scan Time Error Flag                 |    |

|                         | 3-3-6 I/O Verification Error Flag          | 78 |

|                         | 3-3-7 First Scan Flag                      |    |

|                         | 3-3-8 Instruction Execution Error Flag, ER |    |

|                         | 3-3-9 Arithmetic Operation Flags           |    |

|                         | 3-3-10 Clock Pulses                        |    |

|                         | 3-3-11 Special I/O Flags                   |    |

|                         | - PC Link I/O Error Flags                  |    |

|                         | - PC Link Restart Flags                    |    |

|                         | - Remote I/O Error Flag                    |    |

|                         | - SYSNET Error and Run Flags               |    |

|                         | - Host Link Error Flags                    |    |

|                         | - Host Link Restart Flags                  |    |

|                         | 3-4 Holding Relay Area - HR                | !  |

|                         | 3-5 Temporary Relay Area - TR              |    |

|                         | 3-6 Link Relay Area - LR                   |    |

|                         | 3-7 Timer/Counter Area - TC                |    |

|                         | 3-8 Data Memory Area - DM                  |    |

|                         | 3-9 Program Memory - UM                    |    |

|                         | 3-9 Flogram Memory - OW                    |    |

|                         |                                            |    |

| SECTION 4               |                                            |    |

| Programming Instruction | <u>ns</u>                                  | 89 |

|                         | 4-1 Overview                               |    |

|                         | 4-1 Overview                               | 90 |

| ·                       | 4-2 Basic Instructions                     | 90 |

|                         | 4-2-1 LD, OUT, AND, OH, NOT, and END       |    |

L

|                            | 4-8-5 BCD Subt                               | raat                | SUB(31)                                 | 164 |

|----------------------------|----------------------------------------------|---------------------|-----------------------------------------|-----|

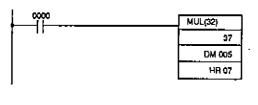

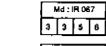

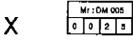

|                            | 4-8-6 BCD Multi                              |                     | MUL(32):                                |     |

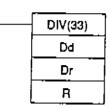

|                            | 4-8-7 BCD Divid                              |                     | DIV(33)                                 |     |

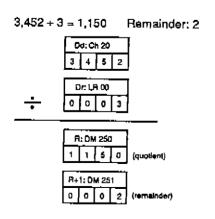

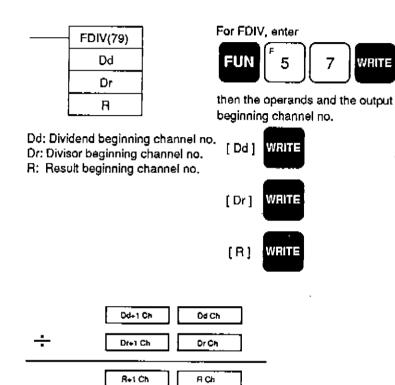

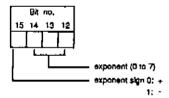

|                            | 4-8-8 Floating P                             |                     | FDIV(79)                                |     |

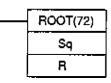

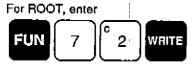

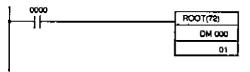

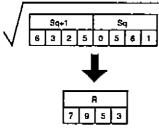

|                            | 4-8-9 Square Ro                              |                     | ROOT(72)                                |     |

|                            |                                              |                     |                                         |     |

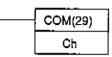

|                            | 4-9-1 Compleme                               |                     | COM(29)                                 |     |

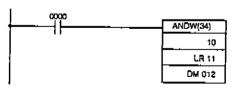

|                            | 4-9-2 Logical At                             |                     | ANDW(34)                                |     |

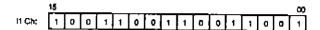

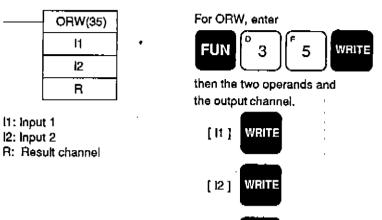

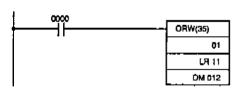

|                            | 4-9-3 Logical O                              |                     | ORW(35)                                 |     |

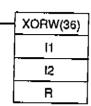

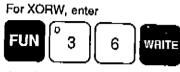

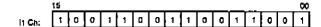

|                            | 4-9-4 Exclusive                              |                     | XORW(36)                                |     |

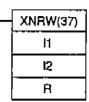

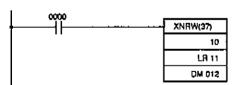

|                            | 4-9-5 Exclusive                              |                     | XNRW(37)                                |     |

|                            |                                              |                     | VIULA1(21)                              | '   |

|                            | 4-10 Special instruction                     |                     | FAL(06)                                 | 103 |

|                            |                                              | arm<br>ailure Alarm | FALS(07)                                | 19/ |

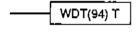

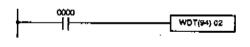

| •                          | 4-10-2 Set Watch                             |                     | WDT(94)                                 |     |

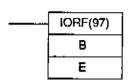

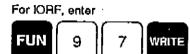

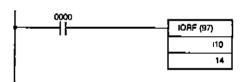

|                            | 4-10-3 I/O Refres                            | -                   | IORF(97)                                |     |

|                            |                                              |                     |                                         |     |

|                            | 4-11-1 Intelligent                           |                     | WRIT(87)                                |     |

|                            | 4-11-2 Intelligent                           |                     | READ(88)                                |     |

|                            | <del>-</del>                                 |                     | NEAD(00)                                |     |

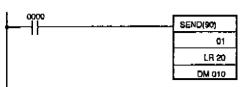

|                            | 4-12-313NET IIISIIOC                         |                     | SEND(90)                                |     |

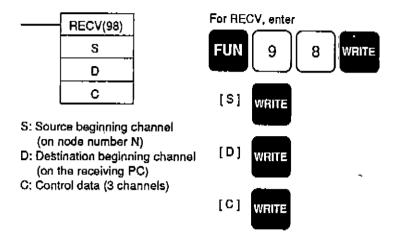

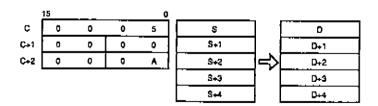

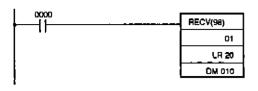

|                            | 4-12-2 Receive                               |                     | RECV(98)                                |     |

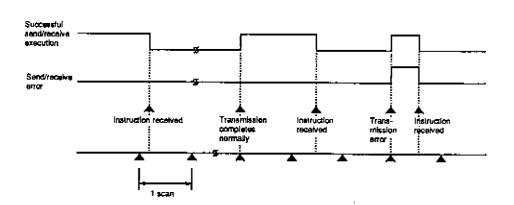

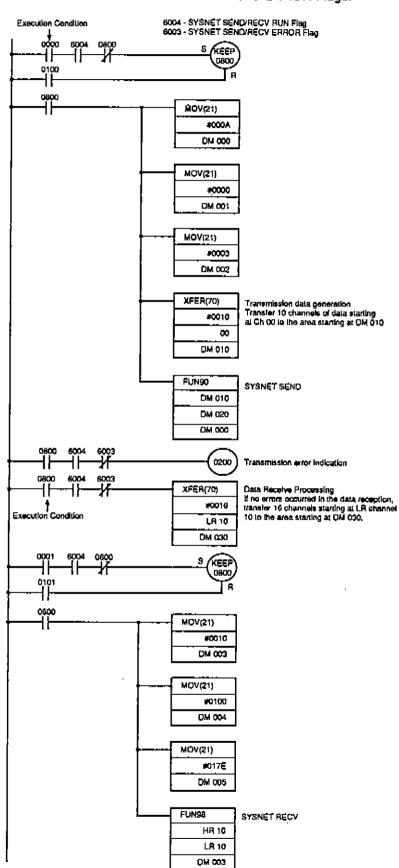

|                            |                                              | PMET Cond and E     | Receive Operations                      |     |

| SECTION 5                  | <u>.                                    </u> |                     | ·                                       | 000 |

| Scan Time and I/O I        | Response Time                                |                     |                                         |     |

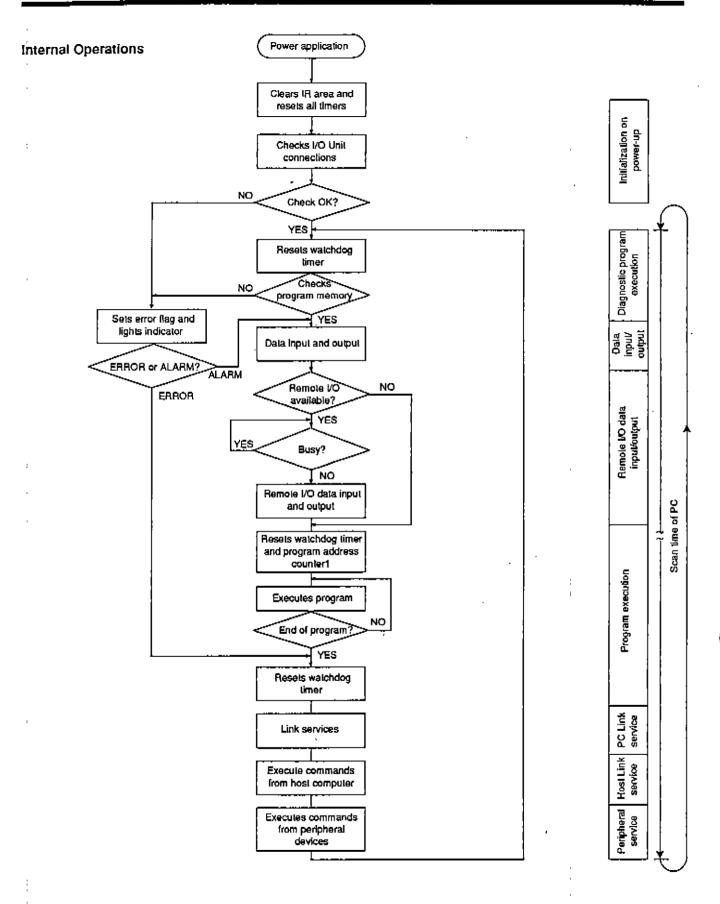

|                            | 5-1 Scan Time and S                          | ystem Reliability   |                                         | 203 |

|                            | •                                            |                     |                                         |     |

|                            | 5-2-1 When Onl                               | ly I/O Units Are Us | sed                                     | 206 |

|                            |                                              |                     | Units, Host Link Units,                 |     |

|                            | and PC Li                                    | nk Units Are Use    | d ,                                     | 208 |

|                            | " '' '                                       |                     |                                         |     |

|                            | 5-4 I/O Response Tin                         | ne                  |                                         | 213 |

| SECTION 6                  | l Troubloobooting                            |                     |                                         | 215 |

| <u>Error wiessages and</u> | ! Troubleshooting                            |                     |                                         |     |

| X.                         | - '                                          |                     | ssages                                  |     |

|                            |                                              |                     |                                         |     |

|                            | •                                            |                     | *************************************** |     |

|                            | <del>-</del> -                               |                     | ······                                  |     |

|                            | •                                            |                     | *************************************** |     |

|                            | 6-6 Troubleshooting.                         |                     | *************************************** | 40  |

| APPENDICES | *************************************** | 229 |

|------------|-----------------------------------------|-----|

| A          |                                         |     |

| В          | Programming Console Operations          | 241 |

| C          |                                         |     |

| D          | Inspection                              |     |

|            | •                                       |     |

| INDEX      |                                         | 261 |

### **SECTION 1**

#### Introduction to Programming

# 1-1 Relay Circuits: The Roots of PC Logic

This chapter introduces the major steps involved in programming. If you are confident with relay ladder diagrams, you may skip over 1-3 Basic Programming Instructions and 1-4 Programming Techniques.

If you're an old hand at relay-based control systems, you'll find a lot that's familiar in the way the Programmable Controller (PC) works. This is because the circuits and internal logic of the PC take the place of the relays, timers, counters, and other formerly discrete devices. The actual operation of the machinery takes place as if those discrete devices were still in place, but with a great deal more flexibility and reliability.

Even though there aren't any actual discrete devices within the PC, the symbols and other control concepts used to describe their operation are still used. These are the basis of the relay ladder diagram programming method. This chapter has been written on the assumption that you are familiar with relay ladder diagrams.

#### Relay Terminology vs. PC Terminology

The terminology used throughout this manual is slightly different from relay terminology, but the concepts are the same. In fact the data areas are even named with relay terminology. Refer to Section 3 for details on the name and purpose of each area.

The following shows the relationship between the relay terminology you may be used to and the PC terminology used for Omron PCs.

| Relay   | PC     |

|---------|--------|

| contact | input  |

| coil    | output |

| relay   | bit    |

In other words, the inputs and outputs referred to in regard to programming are the bits referred to in regard to data areas. This is the same as a relay coil being an output, and the same relay's contacts being inputs (switches) for other devices. (Note that where the word "point" occurs, it refers to an actual point on a Unit attached to the PC.)

## 1-2 Basic Programming Steps

To create a PC control program, follow these basic steps:

- 1. Determine what the controlled system must do and in what order.

- 2. Assign input and output devices to PC I/O bits. That is, designate the external devices that will send signals to and receive signals from the PC.

- Using relay ladder symbols, draw a diagram to represent the sequence of required operations and their inter-relationships.

- If a Programming Console is used, code the ladder symbols into a list of mnemonic instructions so that the program can be input to the CPU.

- 5. Transfer these written instructions to the CPU via the Programming Console, the GPC, FIT, or from a host computer using LSS. (Refer to Appendix A for a brief explanation of these terms.)

- Check for program errors.

- 7. Correct the errors by changing the program.

- 8. Execute the program and test it for execution errors.

- 9. Correct the execution errors by changing the program.

The remainder of Section 1 will focus on Steps 1 through 4.

#### 1-2-1 Assessing the Control Task

Assessing the control task is, of course, a highly important part of setting up a PC controlled system. The PC's flexibility allows a wide latitude in what operations can be controlled, and in how they can be controlled.

To apply the PC to a control task, first determine the system requirements.

#### Input/Output Regulrements

The first thing that must be assessed is the number of input and output points that your system will require. This is done by identifying each device that is to send an input signal to the PC or which is to receive an output signal from the PC. Each input or output point must then be assigned an I/O bit.

Keep in mind that the number of I/O bits available depends on the PC system configuration. (See 3-2 I/O and Internal Relay Area for more details.)

#### Sequence, Timing, and Relationship Assessment

Next, determine the sequence in which control operations are to occur, and the relative timing of the operations. Identify the physical relationships between the controlled devices as well as the kinds of responses that should occur between them.

Each of the related tasks must be similarly determined, from the beginning of the controlled operation to the end.

Having made this assessment, you will be ready to go to step 2 of programming—assigning the input/output devices to I/O bits.

#### Input/Ouptut Assignments

The PC uses the concept of I/O channels. An I/O channel consists of 16 bits.

The four-digit number used to identify an I/O bit, also known as the address of the bit, can be broken down into two parts. The leftmost two digits identify the channel, and the rightmost two digits identify the bit within the channel. See the discussion on addressing conventions in 3-1 I/O Assignments and Data Areas.

#### Assigning Non-I/O IR Bits

Bits that are <u>not</u> used to directly send or receive signals to or from external devices function like the internal relays used in a relay control panel. They are used as data process areas in controlling other bits, timers, and counters. Assign these "internal relays" or work bits when you assign I/O bits during Step 2.

#### Assigning Numbers to Timers and Counters

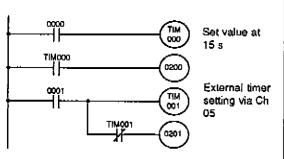

Identify timers and counters with a number that ranges from 000 to 127. When assigning timer and counter numbers, be careful not to use the same timer/counter number for another timer/counter. For example, there cannot be a Timer 001 and a Counter 001.

When you're finished assigning the I/O bits, work bits, and timers/counters, proceed to the next step - drawing the ladder diagram.

#### 1-2-2

#### Drawing the Ladder Diagram

Once you have determined which devices are to be controlled, how they relate to each other, and the sequence (or timing) at which the controlled tasks must take place, write a ladder diagram.

In the ladder diagram, use the four-digit addresses that you assigned to the I/O bits and work bits, as well as the three-digit numbers you gave to the timers and counters. You'll also use relay symbols such as the following.

Relay ladder term: normally open contact

PC term: (normally open) input

Relay ladder term: normally closed contact

PC term: (normally closed) input

Relay ladder term; coil

PC term; output

When you have finished writing your ladder diagram, the next step is to encode the diagram into a language that the PC can understand.

# 1-2-3 Converting the Ladder Diagram Into Mnemonic Code

If you are using a Graphic Programming Console, LSS, or FIT (See Appendix A), you can directly program the PC in ladder diagram logic. However, if you are using the Programming Console, you must convert the ladder diagram into mnemonic code. Mnemonic code consists of addresses, instructions, and data.

"Addresses" in this context refer to program addresses - locations in the PC's program memory where instructions and data are stored. Instructions tell the PC what to do using the operand data that follows each instruction. Each instruction is a step in the program, and address numbers provide a way to reference steps.

When programming, the addresses will automatically be displayed and do not have to be set unless for some reason a different location is desired for the program.

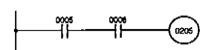

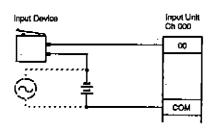

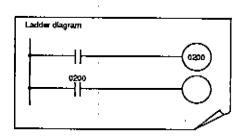

For example, let's consider a mini-program that ANDs two inputs.

Here's the ladder diagram for this.

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | ΓD          | 0005 |

| 0001    | AND         | 0006 |

| 0002    | OUT         | 0205 |

| 0003    | END (01)    | _    |

First, indicate the beginning of the program with LD. In our ladder diagram, the bus bar represents LD. Thus, this instruction is always used when the logic line starts from the bus bar.

Because the first input in the AND circuit must be stored as the data for LD, we write this down in the "data" column on our sheet. In our example, this data is 0005.

The next element of the ladder diagram is AND. The data for AND is the number assigned to the second input, in this case 0006. On our sheet we write this next to AND.

Next, we need OUT to output the result of the AND'd inputs in our circuit. We write this instruction and designate the output to which we want this signal sent. We've chosen this to be 0205 and have written that as the next entry on the sheet. Any I/O bit used with OUT must correspond to an I/O Unit mounted to the PC.

Finally, we program END to tell the PC that the program is over.

# 1-3 Basic Programming Instructions (LD, OUT, AND, OR, NOT, and END)

Except for END, each of these indispensable instructions has a corresponding key on the Programming Console. To enter LD, OUT, AND, OR, or NOT, simply press the appropriate key. END is programmed by pressing the FUN, 0, and 1 keys.

LD and OUT

LD starts each logic line or block. When a logic line starts with an NO (normally open) input, use LD. Use OUT for outputs.

AND

This is used to serially connect two or more inputs.

QR

This is used to connect two or more inputs in parallel.

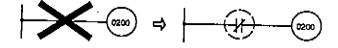

NOT

This inverts its input; often used to form an NC (normally closed) input or output. NOT can be used with LD, OUT, AND, or OR. (NOT is also used when programming differentiated instructions. Refer to Section 4-1-1.)

**END**

This indicates the end of the program. If you forget to include END, the program will not execute and the error message "NO END INST" will be displayed on the LCD of the Programming Console.

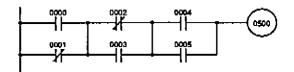

#### 1-3-1 AND LD and OR LD

AND LD connects two blocks in series. In other words, AND LD logically ANDs two blocks. There is no limit to the number of blocks that can be connected together in series with AND LDs.

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD .        | 0000 |

| 0001    | OR          | 0001 |

| 0002    | LD          | 0002 |

| 0003    | OR NOT      | 0003 |

| 0004    | AND LD      |      |

#### **Key Sequence**

The second LD is for the first input in the second block. The AND LD connects these two blocks in series. There are two ways to connect blocks in series.

#### Coding Method #1

| Address | Instruction | Data     |

|---------|-------------|----------|

| 0000    | LD          | 0000     |

| 0001    | OR NOT      | 0001     |

| 0002    | LD NOT      | 0002     |

| 0003    | OR          | 0003     |

| 0004    | AND LD      | <u> </u> |

| 0005    | LD          | 0004     |

| 0006    | OR          | 0005     |

| 0007    | AND LD      | <u> </u> |

|         | :           | :        |

| 0014    | OUT         | 0500     |

#### Coding Method #2

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | <b>L</b> D  | 0000 |

| 0001    | OR NOT      | 0001 |

| 0002    | LD NOT      | 0002 |

| 0003    | OR          | 0003 |

| 0004    | LD          | 0004 |

| 0005    | OR          | 0005 |

|         | :           | :    |

| 0011    | AND LD      | -    |

| 0012    | AND LD      |      |

|         | :           | :    |

| 0014    | OUT         | 0500 |

Using the first coding method, the number of AND LDs is unlimited. When AND LDs are used as in method 2, though, the total number of the LD and LD NOTs before the AND LDs must be eight or less. Therefore, if nine or more are required, use the first coding method.

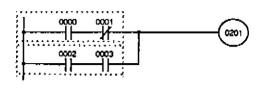

OR LD

OR LD connects two blocks in parallel. In other words, OR LD logically ORs two blocks. There is no limit to the number of blocks that can be connected together in parallel with OR LDs.

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD          | 0000 |

| 0001    | AND NOT     | 0001 |

| 0002    | LD          | 0002 |

| 0003    | AND         | 0003 |

| 0004    | OR LD       |      |

| 0005    | OUT         | 0201 |

**Key Sequence**

The second LD is for the first input in the second block. The OR LD connects these two blocks in parallel. As in the case of AND LD, there are two ways for this to be done.

Coding Method #1

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD          | 0000 |

| 0001    | AND NOT     | 0001 |

| 0002    | LD NOT      | 0002 |

| 0003    | AND NOT     | 0003 |

| 0004    | OR LD       | _    |

| 0005    | LD          | 0004 |

| 0006    | AND         | 0005 |

| 0007    | OR LD       |      |

|         | :           | :    |

| 0012    | OUT         | 0501 |

Coding Method #2

| Address | Instruction | Data     |

|---------|-------------|----------|

| 0000    | ĻD          | 0000     |

| 0001    | AND NOT     | 0001     |

| 0002    | LD NOT      | 0002     |

| 0003    | AND NOT     | 0003     |

| 0004    | LD          | 0004     |

| 0005    | AND         | 0005     |

|         | - :         | *        |

| 0013    | OR LD       | <u>-</u> |

| 0014    | ÖR LD       |          |

|         | į <b>:</b>  | :<br>:   |

| 0019    | OUT         | 0501     |

Again, the same restriction applies as in the case of AND LD. Using the first coding method, the number of OR LDs is unlimited, but when OR LDs are used as in method 2, the total number of the LD and LD NOTs before the OR LDs must be eight or less. Therefore, if nine or more are required, use the first coding method.

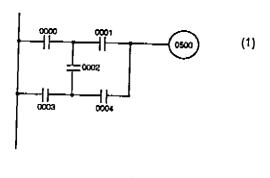

#### 1-4 Programming Techniques

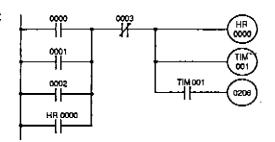

The number of inputs in series or parallel is unlimited. Therefore, use as many inputs as required to configure a clear circuit. Note that any inputs on bridging lines cannot be programmed and therefore must be eliminated.

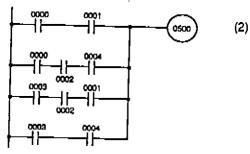

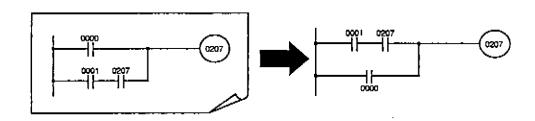

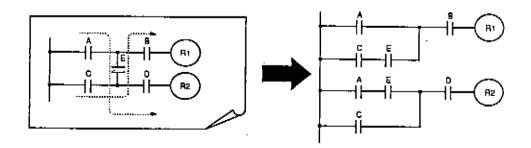

The bridge circuit (1) shown below, for example, should be replaced with the second circuit (2).

Since the number of times I/O bits, work bits, and timers/counters can be used as inputs is not limited, use them as many times as required to simplify your program. Often, complicated programs are the result of attempts to reduce the number of times a bit is used as an input.

Signals always flow from the left bus bar to the right, and the program is always scanned from the top to the bottom.

A logic line cannot start with an output. Use a normally ON SR bit if it is necessary to have an output always ON.

Each logic line starting from the left bus bar must end with an OUT, a timer/counter, or an instruction. The line cannot end with an input. Unlike the actual circuit diagram, the right bus bar need not be written into the ladder diagram.

Since the timers/counters must be assigned numbers from a range of 000 to 127, a convenient way to make this assignment is to begin at one end of the range for timers and the other end for counters. This helps to prevent use of the same number for both a timer and a counter.

Timers/counters cannot directly produce an external output signal but must be programmed to an output with OUT.

The same bit number cannot be assigned as an output more than once. However, an output bit can be later used as an input as many times as desired.

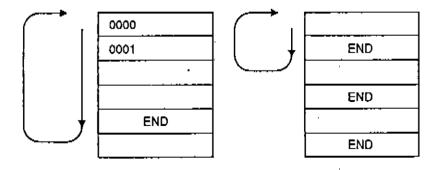

The program is executed from the first program address to the first END. This feature can be used for test runs: divide the program into several blocks by inserting ENDs, then execute the program on a block-by-block basis. When the first block has been checked for correct execution, delete the first END. Continue this process until the program has been completely tested.

1-4-1

Program Organization

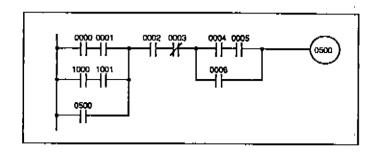

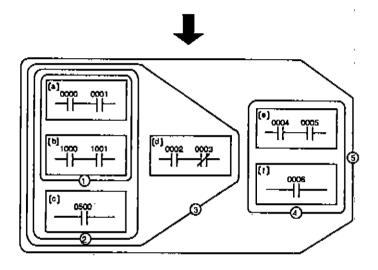

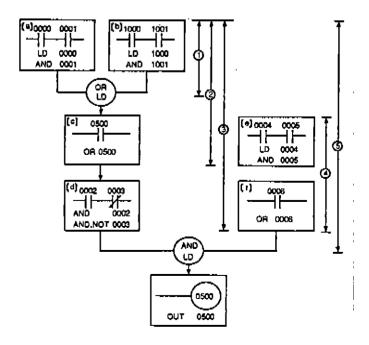

To organize the code for the circuit shown above (1) Divide the circuit into small blocks ([a] to [f]).

(2) Program each block from top to bottom, then from left to right.

#### -Mnemonic Code

|     | Address | instruction | Data |

|-----|---------|-------------|------|

| [a] | 0000    | LD          | 0000 |

|     | 0001    | AND         | 0001 |

| [b] | 0002    | LD          | 1000 |

|     | 0003    | AND         | 1001 |

|     | 0004    | OR LD       | _    |

| [c] | 0005    | OR          | 0500 |

| [d] | 0006    | AND         | 0002 |

|     | 0007    | AND NOT     | 0003 |

| [e] | 8000    | LD          | 0004 |

|     | 0009    | AND         | 0005 |

| [f] | 0010    | OR          | 0006 |

|     | 0011    | AND LD      |      |

| · [ | 0012    | OUT         | 0500 |

## 1-4-2 Programming Examples

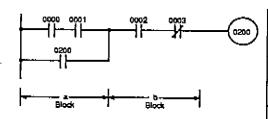

#### (1) Parallel-Series Circult

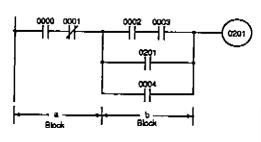

To program a parallel-series circuit, simply program the parallel circuit blocks first, and then the series circuit blocks. In the following example, first program block a, then block b.

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | רם          | 0000 |

| 0001    | AND         | 0001 |

| 0002    | OR          | 0200 |

| 0003    | AND         | 0002 |

| 0004    | AND NOT     | 0003 |

| 0005    | OUT         | 0200 |

#### Series-Parallel Circuit

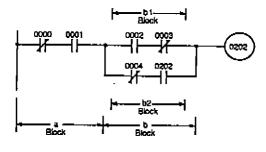

To program a series-parallel circuit, divide the circuit Into the series circuit blocks and parallel circuit blocks. Program each block and then combine the blocks into one circuit. In the following example, divide the circuit into blocks a and b, and program each block. Then combine blocks a and b with AND LD.

| Instruction | Data                        |

|-------------|-----------------------------|

| LD          | 0000                        |

| AND NOT     | 0001                        |

| LD.         | 0002                        |

| AND         | 0003                        |

| OR          | 0201                        |

| OR          | 0004                        |

| AND LD      |                             |

| OUT         | 0201                        |

|             | AND NOT LD AND OR OR AND LD |

The parallel circuit block of the series-parallel circuit shown below can also be divided into two branches. In this case, program block a, and then blocks b1 and b2 in this order. Then combine blocks b1 and b2 with OR LD. Finally, combine block a and block b with AND LD.

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD NOT      | 0000 |

| 0001    | AND         | 0001 |

| 0002    | LD          | 0002 |

| 0003    | AND NOT     | 0003 |

| 0004    | LD NOT      | 0004 |

| 0005    | AND         | 0202 |

| 0006    | OR LD       | _    |

| 0007    | AND LD      |      |

| 0008    | OUT         | 0202 |

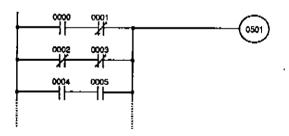

#### Connecting Parallel Circuits in Series

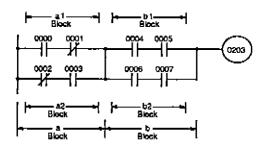

To program two or more parallel circuit blocks in series, first divide the entire circuit into the parallel circuit blocks. Then subdivide each parallel circuit block into the individual blocks. Program each of the parallel circuit blocks, and then combine them in series.

In the following example, program block a1, and then block a2. Then combine both blocks with OR LD. In the same manner, program blocks b1 and b2, and combine them. Finally, combine the two parallel circuit blocks with AND LD.

| Address | Instruction | Data     |

|---------|-------------|----------|

| 0000    | LD          | 0000     |

| 0001    | AND NOT     | 0001     |

| 0002    | LD NOT      | 0002     |

| 0003    | AND         | . 0003   |

| 0004    | OR LD       |          |

| 0005    | LD          | 0004     |

| 0006    | AND         | 0005     |

| 0007    | LD          | 0006     |

| 8000    | AND         | 0007     |

| 0009    | OR LD       | <u> </u> |

| 0010    | AND LD      |          |

| 0011    | OUT         | 0203     |

A series of blocks are programmed in the same way. That is,  $a \rightarrow b \rightarrow (a \cdot b) \rightarrow c \rightarrow (a \cdot b \cdot c) \rightarrow d \cdots$

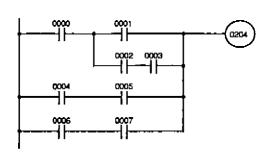

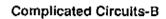

#### Complicated Circuits-A

| Address | Instruction | Data         |

|---------|-------------|--------------|

| 0000    | LD          | 0000         |

| 0001    | ΓĐ          | 0001         |

| 0002    | LD          | 0002         |

| 0003    | AND         | 0003         |

| 0004    | OR LD       | <del>_</del> |

| 0005    | AND LD      | _            |

| 0006    | LD          | 0004         |

| 0007    | AND         | 0005         |

| 8000    | OR LD       | _            |

| 0009    | ß           | 0006         |

| 0010    | AND         | 0007         |

| 0011    | OR LD       | _            |

| 0012    | OUT         | 0204         |

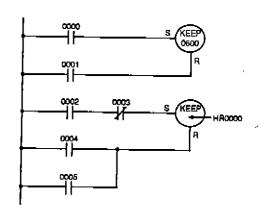

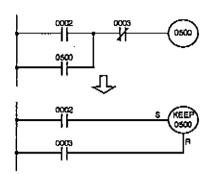

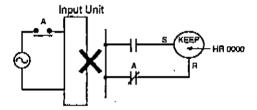

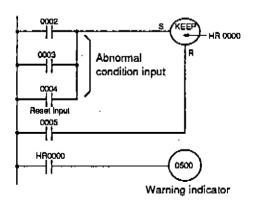

#### The circuit below

```

0002 0003

```

can be thought of as:

or as:

```

0002 0003 0000

```

A complicated circuit can often be simplified by rewriting.

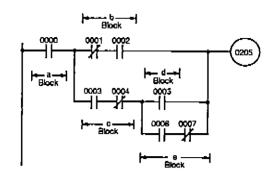

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | ΓD          | 0000 |

| 0001    | LD NOT      | 0001 |

| 0002    | AND         | 0002 |

| 0003    | LD          | 0003 |

| 0004    | AND NOT     | 0004 |

| 0005    | LD          | 0005 |

| 0006    | LD          | 0006 |

| 0007    | AND NOT     | 0007 |

| 8000    | OR LD       |      |

| 0009    | AND LD      | -    |

| 0010    | OR LD       |      |

| 0011    | AND LD      |      |

| 0012    | OUT         | 0205 |

The circuit above can be rewritten as:

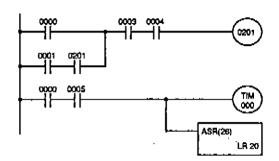

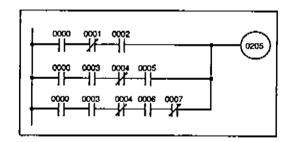

#### Complicated Circuits-C

| Address | Instruction | Dat | a    |

|---------|-------------|-----|------|

| 0000    | LD          |     | 0000 |

| 0001    | OR          |     | 0001 |

| 0002    | OR          |     | 0002 |

| 0003    | OR          | HR  | 0000 |

| 0004    | AND NOT     |     | 0003 |

| 0005    | OUT         | HR  | 0000 |

| 0006    | TIM         |     | 001  |

|         | -           | #   | 0100 |

| 0007    | AND         | ΤIM | 001  |

| 8000    | OUT         |     | 0206 |

Note: A bit in the Holding Relay (HR) area retains its status when a power failure occurs.

#### Problem Circuits to be Avoided

The circuit on the left requires one more program step (an OR LD) than the circuit on the right. By rewriting this code, scan time is saved and program memory space is used more efficiently.

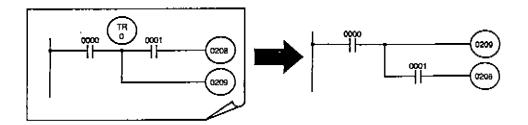

The circuit on the left requires an extra Temporary Relay Area (TR) bit and one more program step (LD) than the circuit on the right. Again, by rewriting this code, scan time is saved and program memory space is used more efficiently.

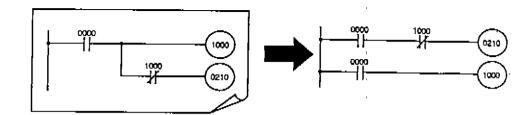

Output 0210 in the circuit on the left cannot be turned ON because of the order in which the PC executes the instructions. By rewriting this code, output 0210 can be turned ON.

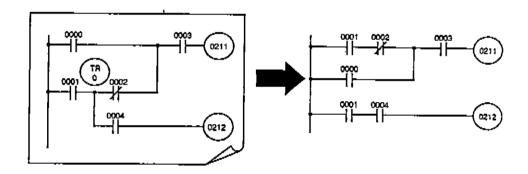

In a circuit with a branch like the one on the left where another input is included, either a TR bit must be used or the circuit must be rewritten as shown on the right.

The circuit on the left cannot be programmed. In order to make the signals flow in the directions indicated by the dotted lines, rewrite the circuit as shown on the right.

#### **SECTION 2**

### Using the Programming Console

This section focuses on how to use the Programming Console to prepare the system for programming, to enter program data, and to monitor system operations and program execution. If you are not using a Programming Console, you can skip this section.

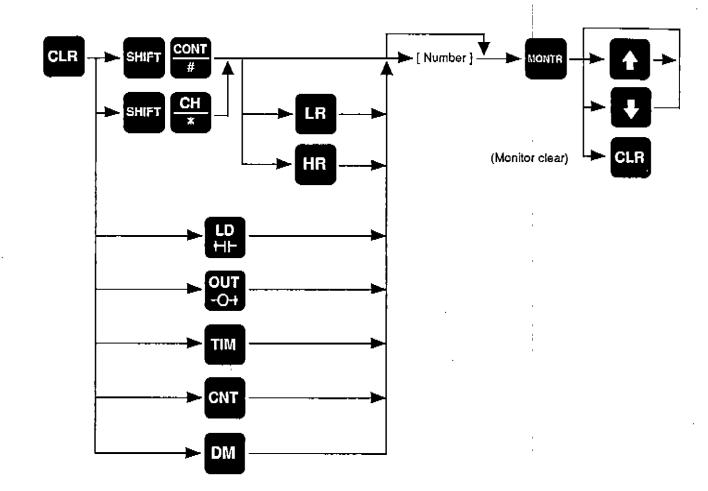

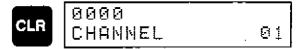

Note: Any of the Programming Console operations described in this section can be cancelled at any time by pressing the CLR key. In some cases, the CLR key may need to be pressed 2 or 3 times.

## 2-1 The Programming Console

The Programming Console is the most commonly used programming device for the C500 PC. It is a compact device that is available either as a hand-held model or for direct mounting to the PC.

Ladder logic program instructions cannot be directly input through the Programming Console. There are, however, other programming devices available as listed in Appendix A.

Refer to each programming device Operation Manual for details about its operations.

#### 2-1-1

#### The Keyboard

The keyboard of the Programming Console is functionally divided by key color into the following four areas:

#### White Numeric Keys

These ten keys are used to input numeric program data such as program addresses, input/output bit numbers and values, and timer/counter numbers and values.

The numeric keys are also used in combination with the function key (FUN) for entering instructions with function codes.

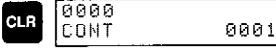

#### Red CLR Key

This key clears the display and cancels current Programming Console operations. It is also used when you key in the password at the beginning of programming operations.

#### Yellow Operation Keys

These yellow keys are used for writing and correcting programs. Detailed explanations of their functions are given later in this section.

#### **Gray Instruction Keys**

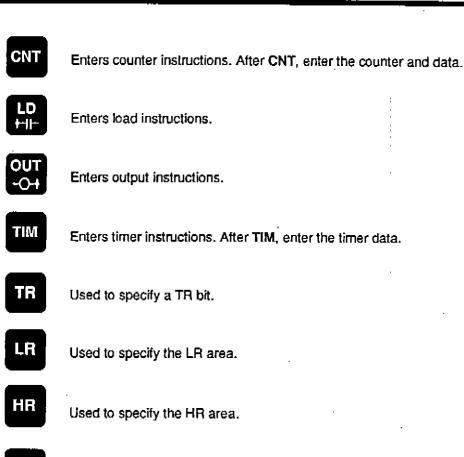

Except for the SHIFT key on the upper right, these gray keys are the ones you'll use to insert instructions into your program. The SHIFT key is similar to the shift key of a typewriter, and is used to obtain the second function of those keys that have two functions.

The remaining gray keys have mnemonic names. The functions of these keys are described below.

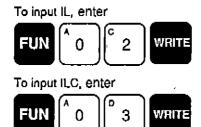

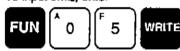

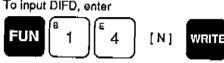

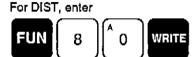

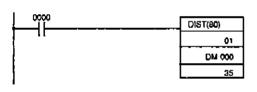

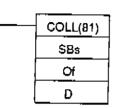

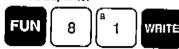

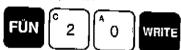

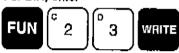

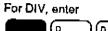

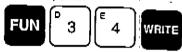

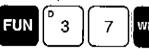

Used to select and enter instructions with function codes. To enter an instruction with function code, press the FUN key and then the appropriate numerical value. Instructions and their function codes are listed in Appendix C.

Enters a shift register instruction.

Inverts the instruction before it. Often used to form a normally closed input or output.

Enters a logical AND instruction.

Enters a logical OR instruction.

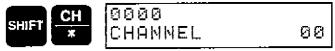

CH Used to specify a channel.

Used to specify the DM area.

$\mathsf{DM}$

CONT

# Used to search for a bit.

2-1-2 The Mode Switch

To select one of three operating modes — RUN, MONITOR, or PROGRAM — use the mode switch.

In RUN mode, programs are executed. When the PC is switched into this mode, it begins controlling equipment according to the program instructions written in its program memory.

Note: Do not leave the Programming Console connected to the PC by an extension cable when in RUN mode.

MONITOR mode allows you to visually monitor in-progress program execution. For instance, if you want to check that a particular input bit is in the correct state at the right time, you can move to the program address (or step) that references that input bit. In MONITOR mode, I/O processing is handled in the same way as in RUN mode.

In PROGRAM mode, the PC does not execute programs. PROGRAM mode is for creating and changing programs, clearing program memory, and registering the I/O table.

#### Mode Changes

The following situations cause the PC mode to change:

#### (1) Peripherals not connected

When power is applied to the PC without a peripheral device connected, the PC is automatically set to RUN mode.

#### (2) Peripherals connected

If the Programming Console is connected to the PC when power is applied, the PC is set to the mode indicated by the Programming Console's mode selector. To be on the safe side, make sure that the PC is in PROGRAM mode when first applying power, in case there is an unknown program in program memory.

If a device such as a Peripheral Interface Unit, P-ROM Writer, or a Printer Interface Unit is attached to the PC when the power is turned on, the PC is automatically set to PROGRAM mode.

Note: If the PC power supply is already turned on when any peripheral device is attached to the PC, the PC stays in the same mode it was in before the peripheral device was attached. The mode can be changed, though, if the Programming Console is attached, with the MODE selector on the front panel of the Programming Console. If it is necessary to have the PC in PROGRAM mode, (for the P-ROM Writer, Printer Interface Unit, etc.), be sure to select this mode before connecting the peripheral device, or alternatively, apply power to the PC after the peripheral device is connected.

### 2-1-3 The Display Message Switch

On the rear of the Programming Console case, on the righthand side of the external connector, there is a small switch for selecting either Japanese or English language messages for display on the console. It is factory set to OFF which causes English language messages to be displayed.

#### 2-2 Preparation for Programming

The following sequence of operations will be performed before beginning actual program input and execution.

Set mode selector to PROGRAM mode.

Enter password.

Clear program memory.

Register the I/O table.

Perform checks until all errors are eliminated.

Each of these operations is described in detail in the following subsections. Except for password entry, all of the other operations are regularly used Programming Console operations. All operations should be done in PRO-GRAM mode unless otherwise noted.

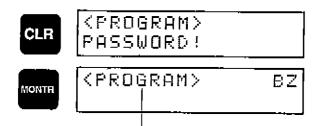

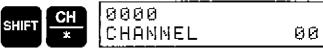

#### 2-2-1 Entering the Password

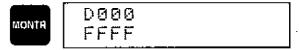

To gain access to the PC's programming functions, you must first enter the password. The password prevents unauthorized access to the program.

The PC prompts you for a password when power is first applied to the PC or after the Programming Console has been connected to the PC. To gain access to the system when the "Password!" message appears on the console, press the CLR and MONTR keys.

Indicates the mode set by the mode selector switch.

Note: The Programming Console displays the current mode in angle brackets (<>). Be sure that the PC is in PROGRAM mode before you enter the password. Then, after you enter the password, you can change the mode to RUN or MONITOR with the mode selector.

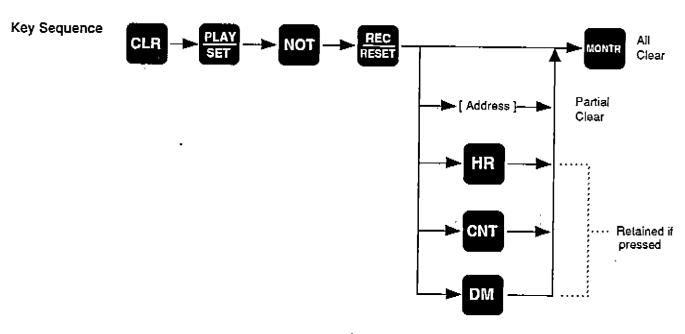

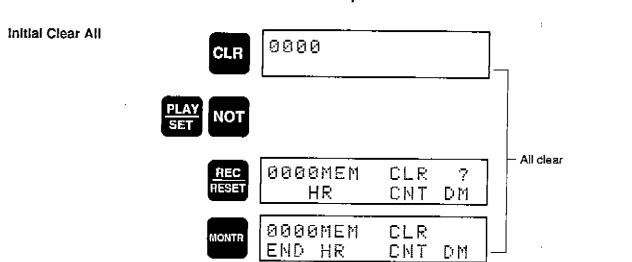

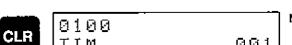

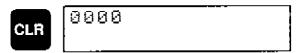

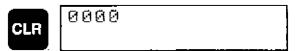

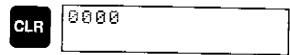

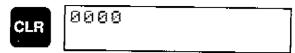

#### 2-2-2 Clear Memory

Using the clear operation it is possible to clear all or part of the IR, HR, DM and TC areas. Unless otherwise specified, the clear operation will clear all memory areas above provided that the Memory Unit attached to the PC is a RAM Unit or an EEP-ROM Unit and the write-enable switch is ON. If the write-enable switch is OFF, or the Memory Unit is a ROM Unit, program memory is not cleared.

Before beginning to program or when installing a new program, clear all areas.

It is possible to retain the data in specified areas when clearing memory. To retain the data in any of HR, TC, or DM press the appropriate key after entering REC/RESET.

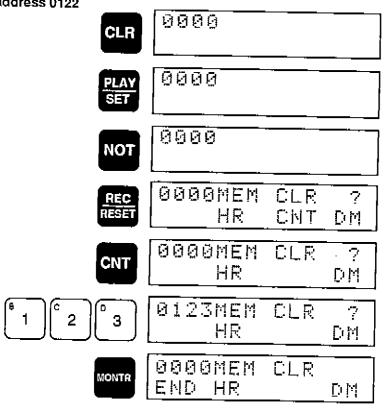

It is also possible to retain a portion of the program memory from the beginning to a specified address. After pressing the REC/RESET key, specify the last address to be retained.

For example, to leave the program data from 0000 to 0122 untouched, but to clear the addresses from 0123 to the end of program memory, key in the address 0123 after pressing the REC/RESET key.

Note: 1. A warning will sound when the memory clear operation is begun.

2. If a mistake is made during input, repeat the operation from CLR.

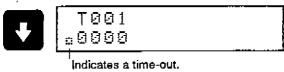

#### Example: Leaving the TC area uncleared and retaining memory up to address 0122

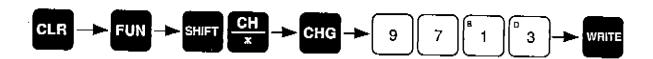

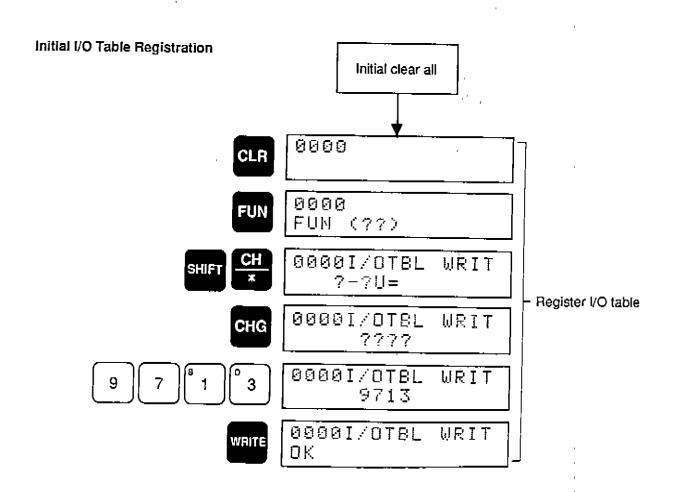

#### 2-2-3 Registering the I/O Table

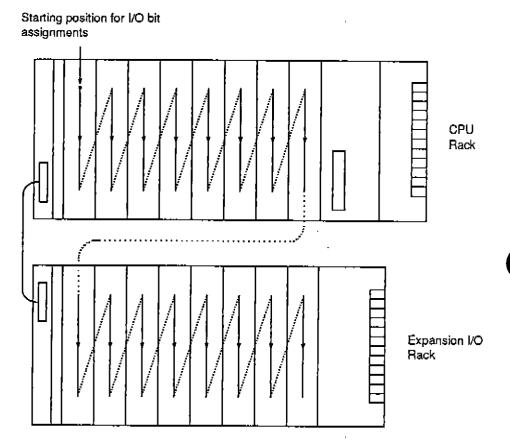

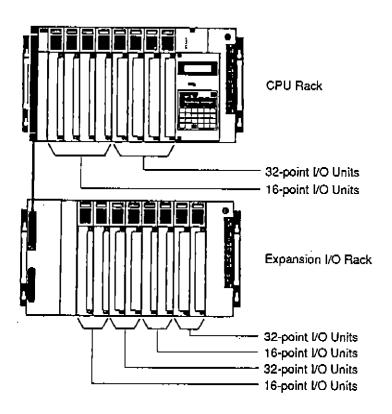

The I/O Table Registration operation writes the types of I/O Units controlled by the PC and the rack locations of the I/O Units into the I/O table memory area of the CPU. It also clears all I/O bits. The I/O table must be registered before programming operations are begun. A new I/O table must also be registered whenever I/O Units are changed because the previous I/O table remains in memory.

I/O Table Registration can be performed only in PROGRAM mode.

The I/O verification error message, "I/O VER ERR," will appear when starting programming operations or after I/O Units have been changed. This error is cleared by registering a new I/O table.

Verliving the I/O Table

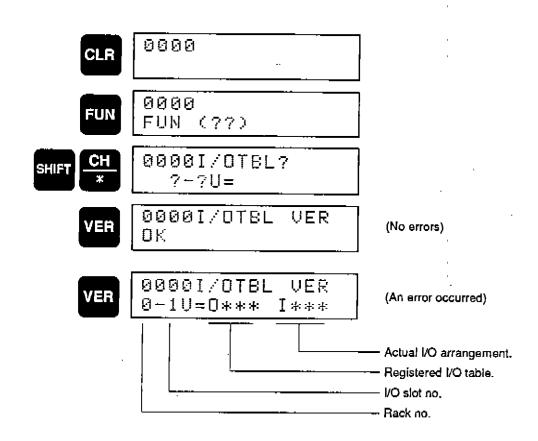

The I/O Table Verification operation is used to check the I/O table registered in memory to see if it matches the actual sequence of I/O Units mounted. The first inconsistency discovered will be displayed as shown below. Every subsequent pressing of the VER key displays the next inconsistency.

**Key Sequence**

Meaning of Displays

Optical Transmitting I/O Unit no. Error

00001/OBTL VER \*\*=R\*-I R\*-W

Duplication

Remote I/O Error

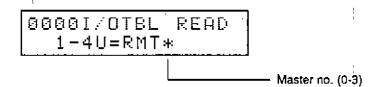

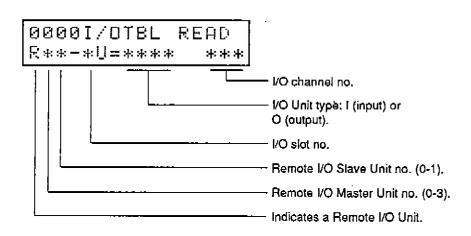

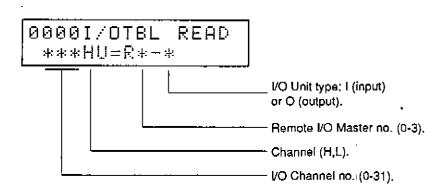

00001/08TL VER \*-\*U=\*\*\*\* RMT\*

This is a Remote I/O Unit that has not been registered.

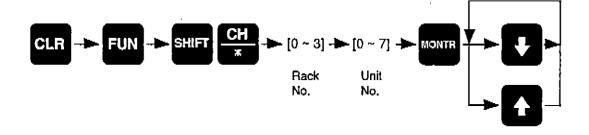

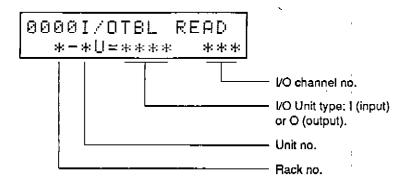

# 2-2-5 Reading the I/O Table

The I/O Table Read operation is used to access the I/O table that is currently registered in the CPU memory.

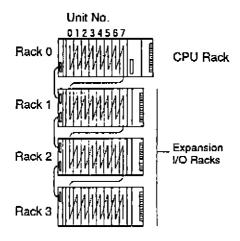

#### Example of I/O Unit Mounting

0000

0000 FUN (??)

SHIFT

0000I/OTBL ? ?-?U=

0000I/OTSL ? 0-7U=

0000I/OTBL READ 0-5U=

0000I/OTBL 7 0-5U=I\*\*\* 05

0000I/OTSL READ 0-4U=I\*\*\* 04

0000I/OTBL READ 0-5U=I\*\*\* 05

#### Meaning of Displays

I/O Unit Designations for Displays

| No. of Points | Input Unit | Output Unit |

|---------------|------------|-------------|

| 16            | I***       | 0***        |

| 32            | II**       | 00**        |

| 64            | IIII       | 0000        |

I/O Units, Special I/O Units,

I/O Link Units

-Remote I/O Master Unit

-Remote I/O Slave Units

Optical Transmitting I/O Units, I/O Link Units, and Remote Terminals

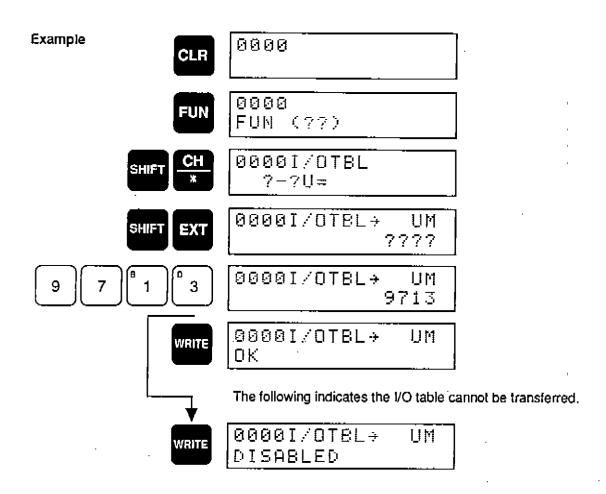

The I/O Table Transfer operation transfers a copy of the I/O table to RAM program memory to allow the user program and I/O table to be written together into EP-ROM.

Note: When power is applied to a PC which has a copy of an I/O table stored in its program memory, the I/O table of the CPU will be overwritten. Changes made in the I/O table do not affect the copy of the I/O table in program memory; I/O Table Transfer must be repeated to change the copy in program memory.

The I/O Table Transfer operation will not work in the following cases:

- 1. When the memory unit is not RAM.

- 2. If there is less than 0.2 KB remaining in program memory.

- 3. If the P-ROM Writer back-panel DIP switch is not set for the C500 (all four pins OFF).

This operation can be done only in PROGRAM mode.

The I/O Table Transfer operation can be performed by inputting 9712 instead of 9713. If it is, the diagnostic check for the battery will not be carried out and the contents of the HR, TC, and DM areas will not be preserved.

## 2-3

#### Programming Operations

The Programming Console operations described in this section can be cancelled by pressing the CLR key.

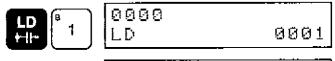

#### 2-3-1

Setting a Program Address

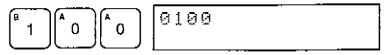

To write, insert, read, or delete program instructions, you must first specify the address at which to read or make changes.

Leading 0s of the address expression need not be keyed in. That is, when specifying an address such as 0053 you need to enter 53 only.

After specifying the address, press the down-arrow key once to display the contents of the address.

#### Key Sequence

| Example    | CLR       | 8999 |

|------------|-----------|------|

| <b>a</b> 1 | 2 D 3 E 4 | 1234 |

|            |           | 1234 |

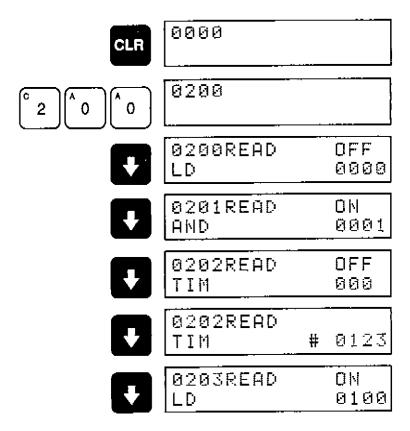

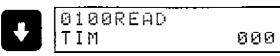

#### 2-3-2 Program Read

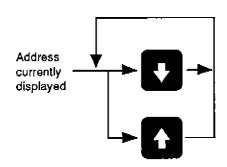

To read out program data from the program memory, specify the address from which to read, then press the down-arrow key.

The down-arrow key must be pressed once to display the contents of a specified address. Then after the specified address contents are displayed, the up and down-arrow keys serve as decremental and incremental data-read keys, respectively. That is, the up-arrow key will display the contents of (current address - 1) and the down-arrow key, the contents of (current address + 1).

#### **Key Sequence**

#### Example

Reading a segment of program code such as the following would result in Programming Console displays that show the program address, instruction, and data for each step that is read.

| Address | Instruction | , C | ata  |

|---------|-------------|-----|------|

| 0000    | LD          |     | 0000 |

| 0001    | AND         |     | 0001 |

| 0002    | TIM         |     | 000  |

|         | ,           | #   | 0123 |

| 0003    | LĎ          |     | 0100 |

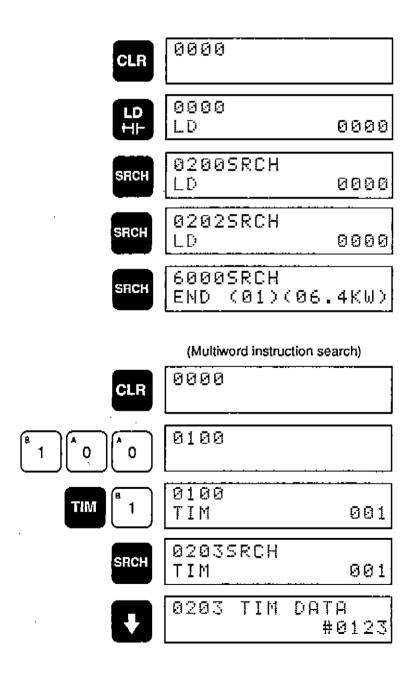

#### 2-3-3 Instruction Search

To search for specific instructions in program memory, first either set a specific address (see 2-3-1 Setting a Program Address) or read through the program (see 2-3-2 Program Read) to the address from which the instruction is to be searched for. Then, specify the particular instruction you wish to search for and press the SRCH key.

This operation can be performed in RUN, PROGRAM or MONITOR mode. While the second LD is being searched for in the example below, the message

| 02005RCH'G |      |

|------------|------|

| LD         | 0000 |

is displayed.

3.8

If the SRCH key is pressed continuously, all the addresses having the specified instruction are successively displayed until either END or the last program memory address is encountered.

To search for the set value of a timer or a counter, first search for TIM or CNT and then use the down-arrow key to access the set value. Note that pressing any key other than SRCH terminates the search operation.

#### Key Sequence

(To search for the set value of a multiword instruction)

#### Example

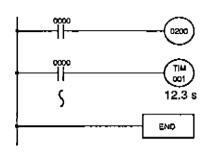

| Address | Instruction | I | Data |

|---------|-------------|---|------|

| 0000    | ĽD          |   | 0000 |

| 0001    | QUT         |   | 0200 |

| 0002    | ΠD          |   | 0000 |

| 0003    | TIM         |   | 001  |

|         |             | # | 0123 |

| :       | :           |   | •    |

| 6000 | END(01) |  |

|------|---------|--|

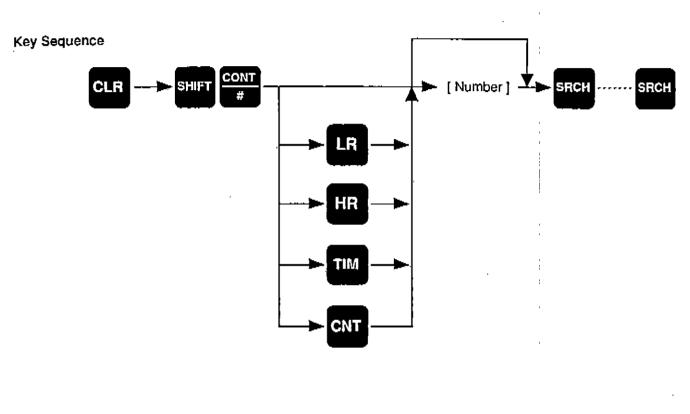

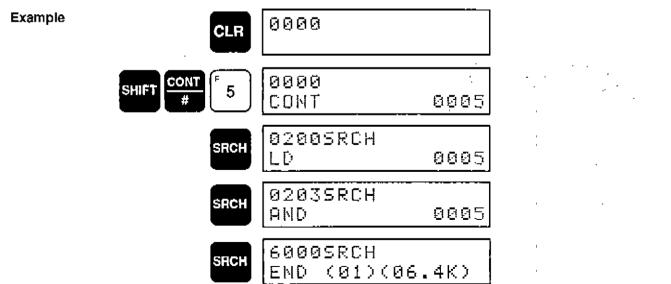

#### 2-3-4 Bit Search

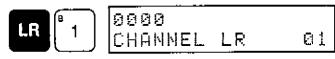

The bit search operation is very similar to the monitor operations described in 2-4 Monitor Operations. To monitor or search, the bit is first specified and then the operation (either monitor or search). To specify an IR, SR, HR, or LR bit (see Section 3 I/O Assignments and Data Areas) or timer/counter within the program, use the SHIFT and CONT/# keys. Then to search, press SRCH.

In the preceding example, the CONT/# key is used in combination with the SHIFT key to specify an IR bit. Then, using the SRCH key, the rest of the program is searched for instructions that use IR bit 0005. When the PC is in the process of searching for another instruction that uses IR bit 0005, the display appears as:

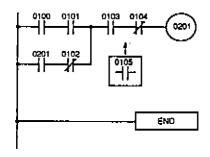

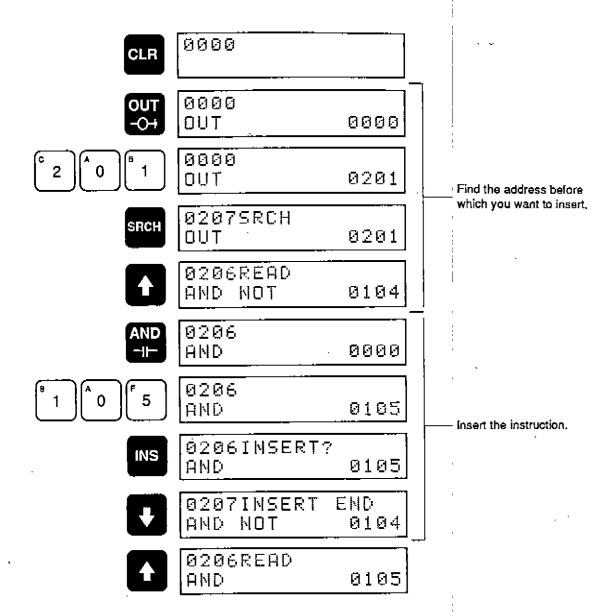

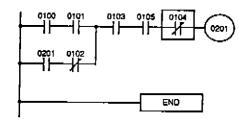

## 2-3-5 Instruction Insert

This operation is used to change a program by inserting an instruction. Instructions cannot be inserted into a program during RUN or MONITOR mode.

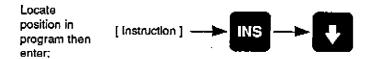

#### **Key Sequence**

#### Example

#### Before Insertion

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | ம           | 0100 |

| 0001    | AND         | 0101 |

| 0002    | LD          | 0201 |

| 0003    | AND NOT     | 0102 |

| 0004    | OR LD       | _    |

| 0005    | AND         | 0103 |

| 0006    | AND NOT     | 0104 |

| 0007    | OUT         | 0201 |

| 0008    | END(01)     |      |

After Insertion

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD          | 0100 |

| 0001    | AND         | 0101 |

| 0002    | LĎ          | 0201 |

| 0003    | AND NOT     | 0102 |

| 0004    | OR LD       | _    |

| 0005    | AND         | 0103 |

| 0006    | AND         | 0105 |

| 0007    | AND NOT     | 0104 |

| 8000    | OUT         | 0201 |

| 0009    | END(01)     | _    |

|         |             |      |

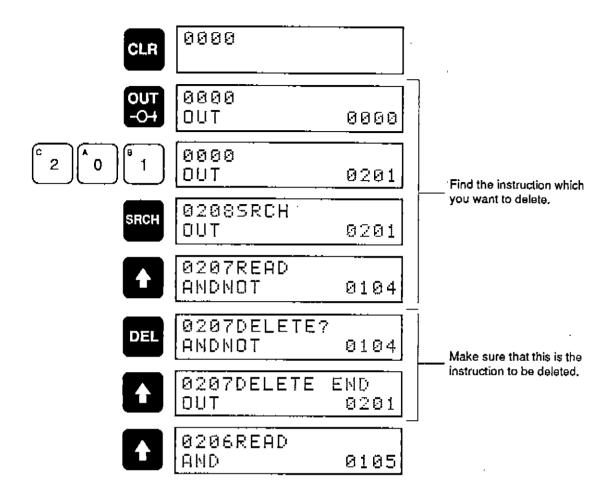

# 2-3-6 Instruction Delete

This operation is used to change a program by deleting an instruction. Instructions cannot be deleted from a program when in RUN or Monitor mode.

#### **Key Sequence**

#### Example

#### Before Deletion

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | TD.         | 0100 |

| 0001    | AND         | 0101 |

| 0002    | LD          | 0201 |

| 0003    | AND NOT     | 0102 |

| 0004    | OR LD       |      |

| 0005    | AND         | 0103 |

| 0006    | AND         | 0105 |

| 0007    | AND NOT     | 0104 |

| 9008    | OUT         | 0201 |

| 0009    | END(01)     |      |

#### After Deletion

| Address | Instruction | Data |

|---------|-------------|------|

| 0000    | LD          | 0100 |

| 0001    | AND         | 0101 |

| 0002    | LD          | 0201 |

| 0003    | AND NOT     | 0102 |

| 0004    | OR LD       | _    |

| 0005    | AND         | 0103 |

| 0006    | AND         | 0105 |

| 0007    | OUT         | 0201 |

| 0008    | END(01)     | _    |

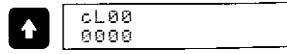

When you delete an instruction, you must first read it before deleting it. The actual deletion is accomplished by pressing the up-arrow key.

The program addresses following the deleted instruction are automatically decremented. So, after a deletion, the next address will be displayed and can be easily deleted. In this way, a number of instructions can be quickly deleted by repeatedly pressing the up-arrow key.

Be careful not to inadvertently delete instructions.

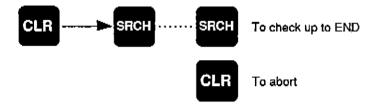

#### 2-3-7 Program Check

This operation does a syntax check on a program. When a program has been changed in any way, it should first be checked for programming errors before execution. A program can be checked only in PROGRAM mode.

#### **Key Sequence**

Note: Refer to 6-5 Program Errors for the error displays and their meanings.

Pressing the CLR key during a program check cancels the check (display #1).

Use the SRCH key to display the addresses of offending instructions and the data they contain. To successively check the program up to END, hold down the SRCH key (display #2).

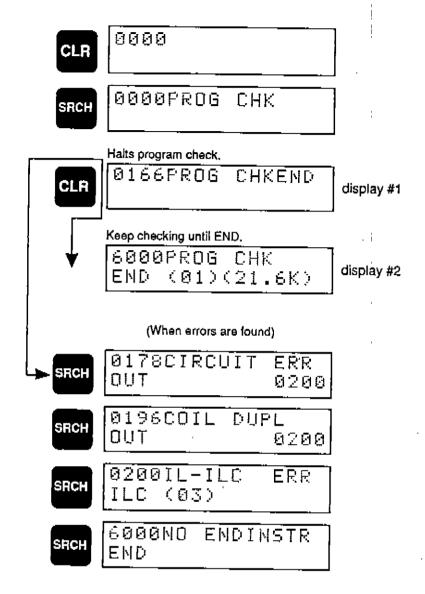

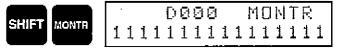

#### 2-3-8 Scan Time Read

To display the current scan time, enter CLR then MONTR. See Section 5 Scan Time and I/O Response Time for details.

Note that the time displayed by this operation is an average scan time. The differences in displayed values depend on when the MONTR key is pressed.

This operation is available only when the PC is in RUN or MONITOR mode. Also, the scan time will not be displayed if the program is stopped.

#### Example

#### 2-3-9 Error Message Read

When an error occurs during program execution, it can be displayed for identification by pressing CLR, FUN, and then MONTR. If an error message is displayed, press the MONTR key to clear the error. Sometimes a beeper will sound and the error cannot be cleared. If this happens, take the appropriate corrective action (see Section 6 Error Messages and Troubleshooting) to eliminate the error.

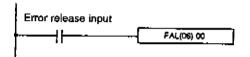

When several errors occur, the respective error messages can be displayed by pressing the MONTR key. The sequence in which error messages are displayed depends on the priority levels of the errors. The following highest priority errors cause the CPU to halt.

MEMORY ERR

NO END INST

I/O BUS ERR

I/O SET ERR (Rack number)

I/O UNIT ERR

SYS FAIL FALS (Number)

The next group of errors do not stop the CPU.

SYS FAIL FAL (Number)

DPL ERR

REMOTE I/O ERR (Remote I/O Unit no.)

I/O VER ERR

SCAN TIME OVER

#### 2-4 Monitor Operations

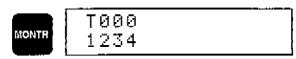

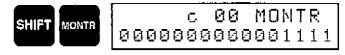

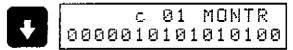

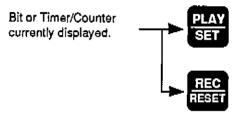

The monitor operation allows you to monitor bits, channels, or timers/counters and it supplements the functions provided by the Program Read, Instruction Search, and Bit Search operations described in previous subsections. In all cases, monitoring involves specifying the bit, channel or timer/counter to be monitored and then pressing the MONTR key.

The monitor operation described in this section may be performed in RUN, MONITOR, or PROGRAM mode and can be cancelled by pressing the CLR key.

#### 2-4-1 General Status Monitoring

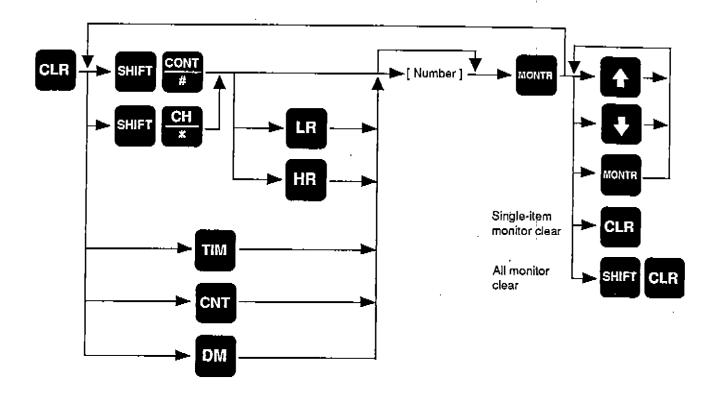

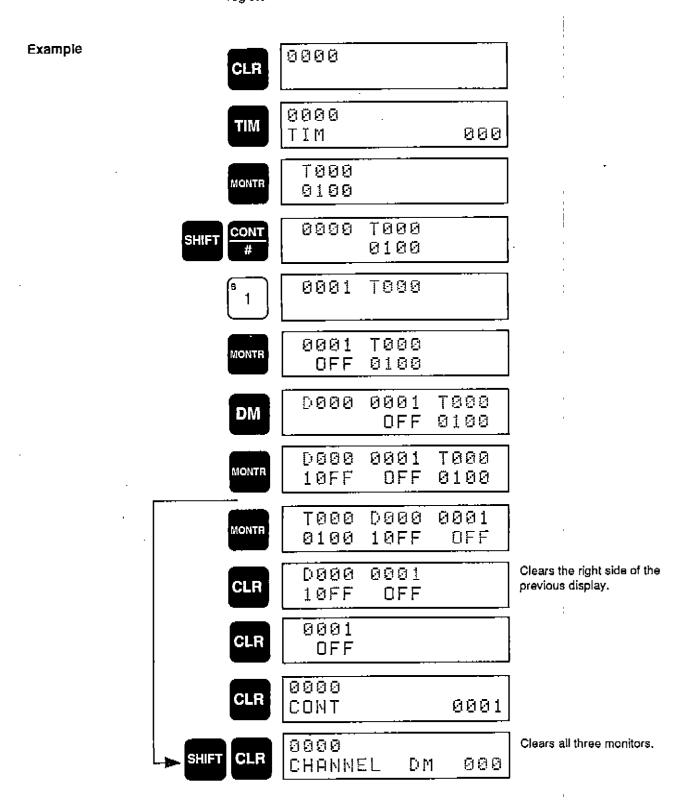

To monitor the status of an IR, SR, HR, or LR bit or channel, or a DM channel, specify the desired data, then press the MONTR key. Likewise, to monitor the set value of a timer or a counter, specify the desired timer/counter then press the MONTR key.

Using this operation you can simultaneously monitor the status of up to six values (any of channels, timers/counters, or bits). Of these 6 values, 3 are displayed at any one time. The 3 values selected for display may be changed at will and information is lost only if a 7th value is selected for monitoring, in which case the first value selected is lost and the 7th is read. This monitoring process can be continued for as long as desired.

The monitor value displayed in the leftmost corner can be force-set or, if it is channel data or a present value, can be changed.

Bit monitor displays indicate the ON/OFF status of the bit in question. Channel monitor displays show the binary (see 2-4-3), or hexadecimal contents of the specified channel. Timer/counter monitor displays show the BCD present value and a ":::" in the lower left-hand corner when the present value (PV) has become 0.

By pressing the up-arrow and down-arrow keys, the display bit number or channel number is automatically incremented or decremented.

#### Examples

#### Program Read then Monitor

TIM

Monitor Clear

991

**Bit Monitor**

**Channel Monitor**

| STONITO | cL01 |  |

|---------|------|--|

| MONTA   | FFFF |  |

#### Multiple Monitoring

As shown in the next example, the first bit's status gets shifted to the right when other bits are monitored. If more than three bits are monitored, the bit monitored first gets shifted off the display but is still stored in the internal register.

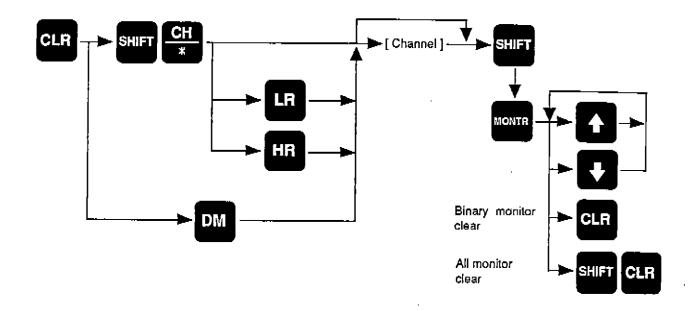

#### 2-4-2 Displaying a Single Channel in Binary

You can specify that the contents of a monitored channel be displayed in binary by pressing the SHIFT and MONTR keys after the channel number has been input. Channels can be successively monitored by using the up-arrow and down-arrow keys to increment and decrement the display channel number. To clear the binary display press the CLR key.

#### Example

| 01.0 | 0000 |

|------|------|

| GLH  | FFFF |

SHIFT CLR CLR G000 CHANNEL DM 000

# 2-5 Data Modification Operations

These operations are used to change channel data, to assign new set values and present values to timers and counters, and to set/reset bits. Except for the Hex <-> ASCII change operation, data modification operations can be done only in PROGRAM and MONITOR modes.

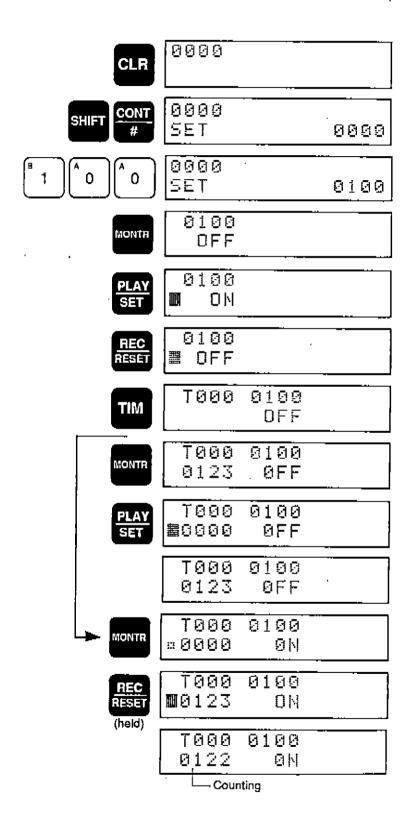

#### 2-5-1 Force Set/Reset

This operation force sets and resets IR, SR, HR, and LR bits. It can also be used to force set/reset timers and counters.

#### **Key Sequence**

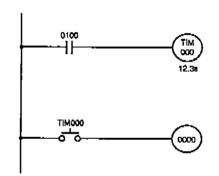

#### **Programming Example**

| Address | Instruction | Da  | ta   |

|---------|-------------|-----|------|

| _0000   | LD          |     | 0100 |

| 0001    | TIM         |     | 000  |

|         |             | #   | 0123 |

| 0002    | LD          | ТІМ | 000  |

| 0003    | OUT         |     | 0000 |

Example/s were to a selfsaft not have to selfwhote the Addresses will be counted down and consecutive bits set/reset as long as the PLAY/SET or REC/RESET key is held down. Channels 61 through 63 cannot be reset. Attempts to do so will activate a beeper.

#### 2-5-2 PV Change 1

This operation changes the BCD present value of timers and counters. It also can be used to assign a new 4-digit decimal or hexadecimal value to an IR, HR, LR, or DM channel.

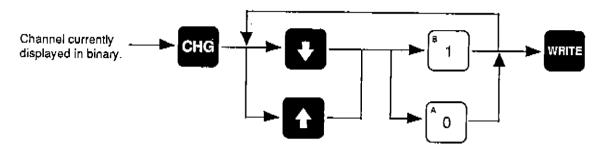

2-5-3 PV Change 2

This operation assigns a new 16-digit binary value to an IR, HR, LR, or DM channel.

Example

The blinking square which can be shifted to the left with the up-arrow key and to the right with the down-arrow key, indicates the position of the bit that can be changed. After positioning to the desired bit, a 0 or a 1 can then be entered as the new bit value. After a bit value has been changed, the blinking square will appear at the next position to the right of the changed bit.

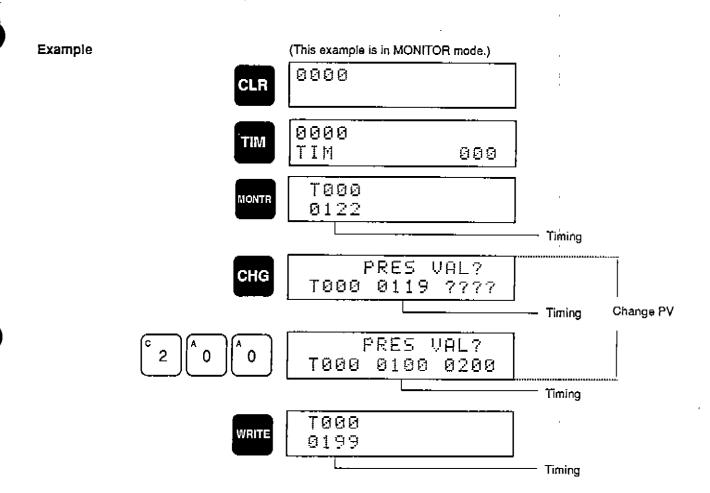

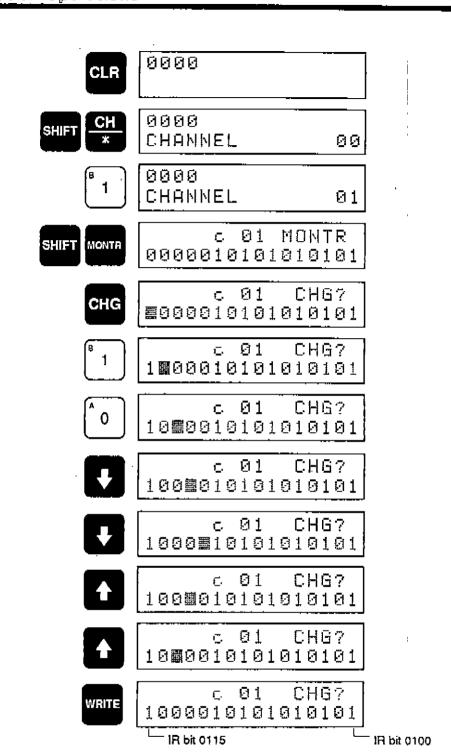

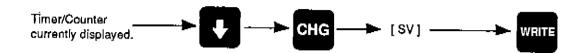

2-5-4 Timer/Counter SV Change 1

This operation changes the set value of a timer or counter while the program is being executed. This operation must be done in either MONITOR or PRO-GRAM mode.

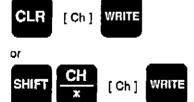

#### **Key Sequence**

#### Example 0000 0000 $\mathsf{TIM}$ TIM 000 92015RCH SRCH TIM 000 TIM 0201 DATA #0123 0201 TIM DATA CHG T000 #0123 #???? 0201 TIM DATA T000 #0123 #0124 9291 DATA? T000 #0123 6777 0201 DATA? T000 #0123 Ċ. 10 9201 TIM DATA 10

#### 2-6 Cassette Tape Operations

PC programs (from user program memory-UM) or DM data may be backed-up on a standard commercially available cassette tape recorder. Any kind of magnetic tape of adequate length will suffice. (Note: To save an 8-Kword program, the tape must be 15 minutes long.) Always allow about 5 seconds of blank tape leader before the taped data begins. Store only one program on a single side of a tape; there is no way to identify separate programs stored on the same side of the tape.

Use patch cords to connect the cassette recorder earphone (or LINE-OUT) jack to the Programming Console EAR jack and the cassette recorder microphone (or LINE-IN) jack to the Programming Console MIC jack. Set the cassette recorder volume and tone controls to maximum levels.

Note: For all operations, saving, loading, and verifying:

The PC must be in the PROGRAM mode.

While the operation is in progress, the cursor blinks and the block count is incremented on the display.

Operation may be halted at any time by pressing the CLR key.

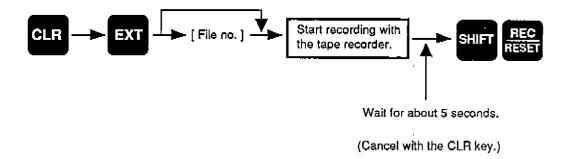

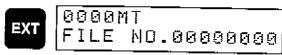

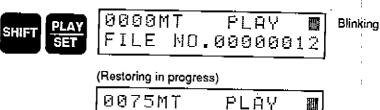

#### 2-6-1 Saving a Program

to Tape

This operation copies program data from UM onto the cassette tape.

The procedure is as follows:

Select a file number for the data that is to be saved. Start cassette tape recording.

After about 5 seconds, press the SHIFT and RESET keys.

Program saving continues until END is reached. At that time the program size in Kwords is displayed.

Example

Start recording with the tape recorder.

Let it run for about 5 seconds.

(Recording in progress)

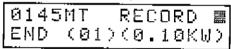

| 0075MT  | RECORD    | 噩  |

|---------|-----------|----|

| FILE MO | 1.9999991 | 2, |

(When it comes to END)

| 0145 | MT   | REC | ORD  | 豊 |

|------|------|-----|------|---|

| END  | (01) | (01 | .0KW | ) |

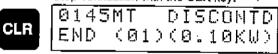

Stop recording with the CLR key.

| SCONTO |

|--------|

|        |

| 1.0KW) |

|        |

(Saved up to END.)

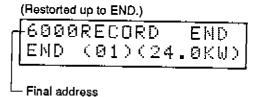

6000RECORD EMD END (01)(24.0KW)

- Final address

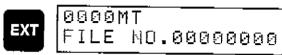

## 2-6-2

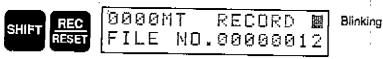

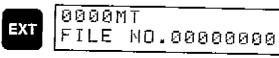

#### Restoring Program Data

This operation restores program data from a cassette tape and writes it to user program memory (UM).

The procedure is as follows:

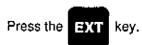

Press the EXT key.

Specify the number of the file to be restored.

Start playing the cassette tape.

Within 5 seconds, press the SHIFT and FLAY keys to restore data.

Program restoration continues until END is reached, at which time the program size in Kwords is displayed.

To restore program data recorded on two sides of a tape or on two or more tapes, begin restoring from the lowest address.

Example

Start the tape recorder playing

Within 5 seconds...

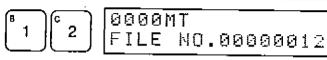

FILE NO.00000012

(When it comes to END) 0145MT RECORD END (01)(01.0KW)

CLR EMD (01)(01.0KW)

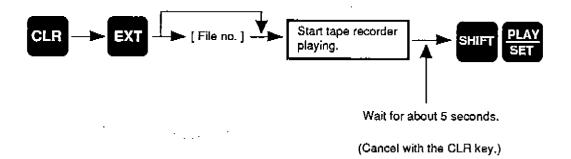

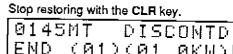

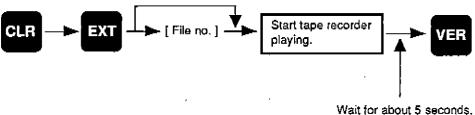

### 2-6-3 Verifying Program Data

This operation verifies that the contents of user program memory (UM) and the cassette tape program data match.

The procedure is as follows:

Press the **EXT** key.

Specify the number of the file to be verified.

Start playing the cassette tape

Within 5 seconds, press the VER key to verify data.

Program verification continues until END is reached, at which time the program size in Kwords is displayed.

To verify program data recorded on two sides of a tape or on two or more tapes, begin verifying from the lowest address.

#### **Key Sequence**

vvait for about 5 seconds.

(Cancel with the CLR key.)

Example

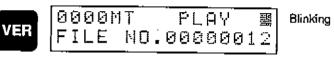

Start the tape recorder playing

Within 5 seconds...

(Verification in progress)

| 0075M |     | PLAY    |   |

|-------|-----|---------|---|

| FILE  | MO. | 0000001 | 2 |

(When it comes to END)

Stop verification with the CLR key.

(Verified up to END.)

6000RECORD END END (01)(24.0KW)

Final address

## **SECTION 3**

## 3-1 Overview

This section explains how I/O bits are used to identify individual I/O terminals and discusses the functions of the various types of data areas in the PC.

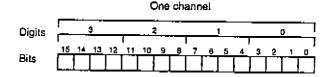

**I/O Channels**

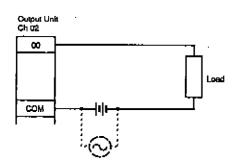

The PC operates by monitoring input signals from such sources as push-buttons, sensors, and limit switches. Then, according to the program in its memory, the PC reacts to the inputs by outputting signals to external loads such as relays, motor controls, indicator lights, and alarms.

I/O channels are used to identify the input/output bits that correspond to the external terminal points through which the PC interacts with physical devices. Each channel consists of 16 bits. The I/O bits are assigned addresses as follows.

#### **Addressing Conventions**

Channel numbers are two-digit expressions and bit numbers are also two-digits. Thus four digits are used to address a particular I/O bit. Examples of I/O channel/bit addresses are shown below.

| I/O Channel # + Bit # (0 - 15) - I/O address |                    |    |               |      |  |  |

|----------------------------------------------|--------------------|----|---------------|------|--|--|

| Channel 16, bit 3:                           | nnel 16, bit 3: 16 |    |               | 1603 |  |  |

| Channel 3, bit 15:                           | 03                 | 15 | $\rightarrow$ | 0315 |  |  |

Like I/O channel addresses, data area locations are also referenced by specifying a channel number and a bit number.

When the data is read as a four-digit decimal or hexadecimal number, each digit represents a set of four bits in the channel (16 bits in all). Therefore, the rightmost digit of the decimal or hexadecimal number represents the rightmost four bits (3 to 0) of the channel.

If, for example, the ON/OFF status of the rightmost four bits is 0101 in binary, the corresponding digit would be 5 in decimal or hexadecimal. In the case where the ON/OFF status is 1111 in binary, the hexadecimal number would be F (decimal 15).

ÖV9rvi⊕w SECTION 3-1

#### Types of Data Areas

I/O channel bits are part of the I/O and Internal Relay (IR) Area. Bits that are not used for actual input or output operations constitute the remaining part of IR and are referred to as "work" bits. These work bits do not control external devices directly, rather they are used as data processing areas to control other bits, timers and counters.

Timers and counters are found in the Timer/Counter (TC) area. The Special Relay (SR) area is used for system clocks, flags, and status information.

There is also a Link Relay (LR) area for inter-PC communication in systems that employ PC Link Units.

The function of the Holding Relay (HR) area is to store data and to retain the data values when the power to the PC is turned off. Data Memory (DM) is also used for internal data storage and manipulation and its values are also retained when power is off, but, unlike the HR area, it is only accessible in channel units. TR bits are used for temporary storage.

The programs that control the PC and all of its input and output operations are stored in the User Program Memory (UM). The capacity of the program memory depends on the type of RAM or ROM mounted to the CPU.

The following table shows the bits allocated within the PC.

| Area      | Bit Address Range           |

|-----------|-----------------------------|

| 1/0       | 0000 to 3115                |

| Work Bits | 3200 to 6002                |

| SR        | 6003 to 6307                |

| TR        | TR 0 to TR 7                |

| HR        | HR 0000 to HR 3115          |

| LR        | LR 0000 to LR 3115          |

| T/C       | 000 to 127 (channels)       |

| DM        | DM 000 to DM 511 (channels) |

Note: IR bits not used for I/O and also bits which are not used in other areas can be used as work bits.

3-2 I/O and Internal Relay Area - IR

The I/O and Internal Relay Area (IR) is used for both I/O and internal data storage and manipulation. The channels available for I/O are as indicated in the table below.

Note that the actual number of IR channels that can be used as I/O channels is determined by the model of the CPU and the hardware configuration of the PC system.

I/O Channels

|      |      |      |      |      | Char | nel No | ımber |      | -    |      | ·    | _    |

|------|------|------|------|------|------|--------|-------|------|------|------|------|------|

| 00Ch | 01Ch | 02Ch | 03Ch | 04Ch | 05Ch |        | 26Ch  | 27Ch | 28Ch | 29Ch | 30Ch | 31Ch |

| 00   | 00   | 00   | 00   | 00   | 00   | ]      | 00    | 00   | ÓQ   | 00   | 00   | 00   |

| 01   | 01   | 01   | 01   | 01   | 01   |        | 01    | 01   | 01   | 01   | 01   | 01   |

| 02   | 02   | 02   | 02   | 02   | 02   |        | 02    | 02   | 02   | 02   | 02   | 02   |